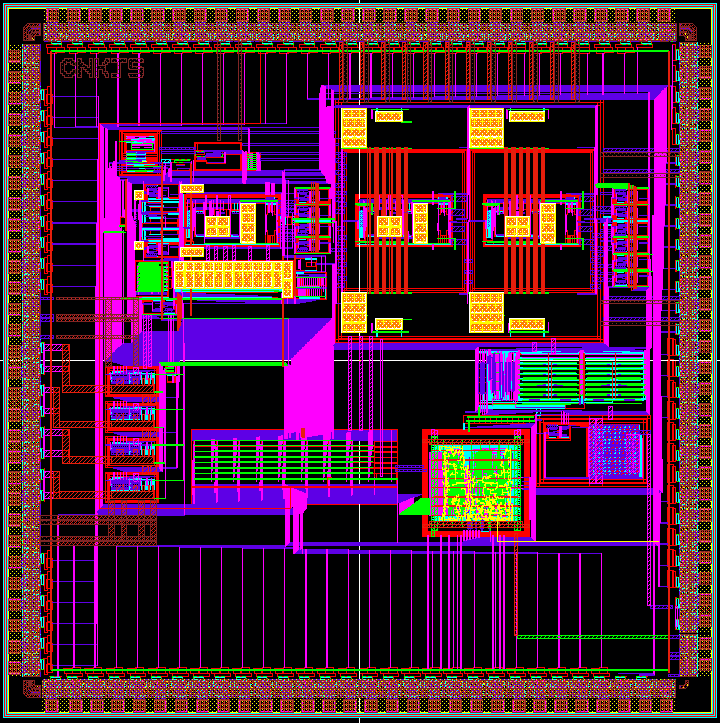

| IP개요 |

A low-noise incremental Delta–Sigma Capacitance to Digital Converter(CDC) integrated circuit (IC) for capacitive microsensors is presented. In the conventional CDC, two-step conversion schemes including capacitance to voltage converter and voltage to digital converter are generally used. The presented Delta-Sigma CDC can convert the capacitance changes to the digital codes directly. The Delta-Sigma schemes are widely used for low noise applications due to the Delta-Sigma modulator’s ability to reduce in-band white noise by the inherent noise shaping characteristic. The low frequency colored noises such as flicker (1/f) noises still remain. In order to reduce the low frequency colored noise component, a chopper stabilization technique is exploited to the SC integrator of the Delta-Sigma CDC. The integrated circuit is implemented in a 0.18-μm standard CMOS process. The proposed incremental Delta–Sigma CDC consumes 1.12-mW of power from a 3.3-V supply at a sampling frequency of 500-kHz. |