| IP개요 |

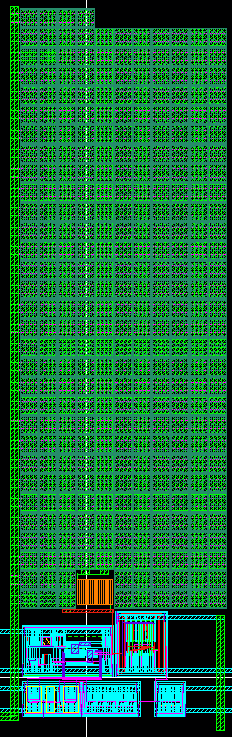

To reduce the phase noise and jitter of the conventional PLL, the proposed PLL uses frequency voltage converter (FVC). When the output voltage (VCO input voltage) of the loop filter changes, the output voltage of the FVC changes in the opposite direction at a much higher sampling frequency in the negative feedback looped VCO. Thus, Whenever the VCO output frequency varies, the FVC works as a compensator and it results in VCO noise reduction. It has been simulated and proved by HSPICE in a CMOS 0.18μm 1.8V process |