| IP명 | 16Gbps Half-rate Reference-Less Sub-sampling based Clock and Data Recovery Circuit using Stochastic Frequency Locked Loop | ||

|---|---|---|---|

| Category | Analog | Application | Wireline interface |

| 실설계면적 | 2㎛ X 1㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 8GHz |

| 검증단계 | Silicon | 참여공정 | HM-2301 |

| IP개요 | Stochastic 방식의 FLL과 Sub-sampling 방식의 PLL을 사용한 CDR이다. 설계된 CDR은 기준 신호가 없는 타입이며 오로지 데이터로만 클록을 복원시킨다. 주파수 고정 루프는 Stochasitc 방식을 사용하였으며 기존 연구와 달리 디바이더의 단수를 줄여서 다지인의 복잡도와 락 타임을 줄였다. |

||

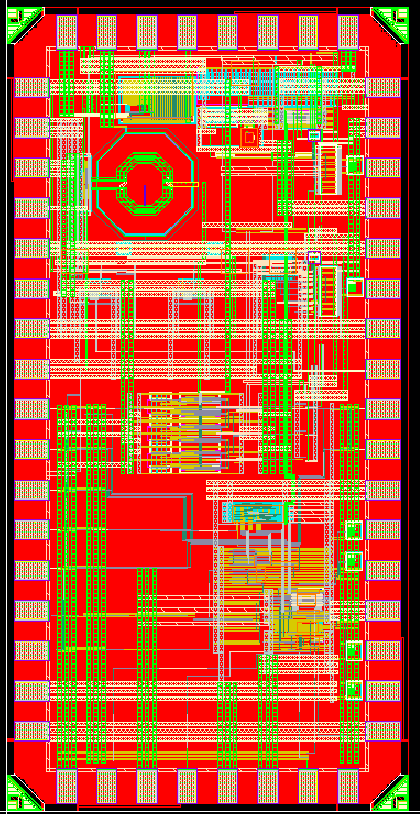

- 레이아웃 사진 -

|

|||