| IP개요 |

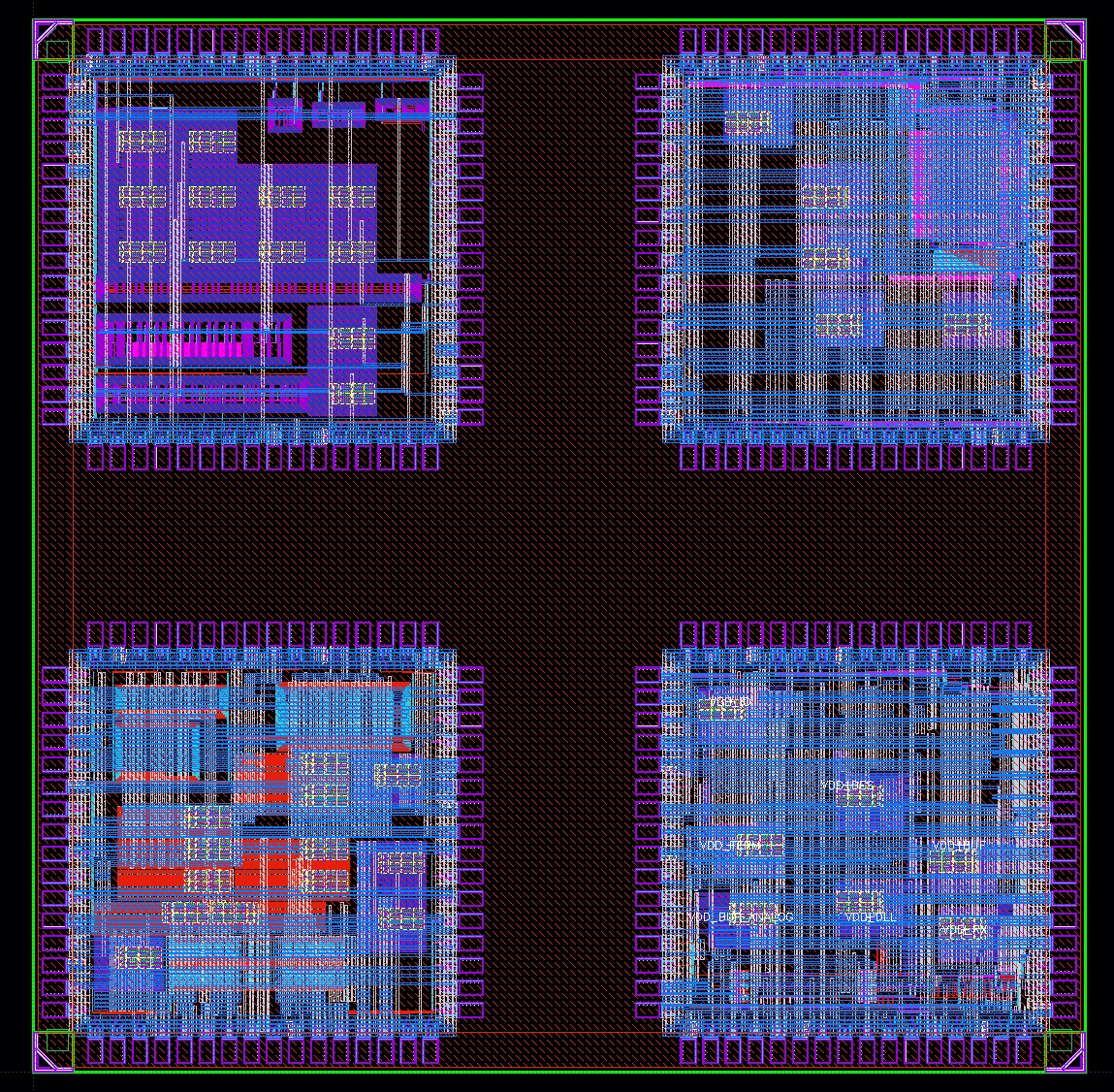

본 설계계획서는 energy-efficient ADC-less Analog in-memory computing SRAM array 기반 multilayer perceptron 회로를 제안한다. 제안된 회로는 binary weight을 사용하는 196-128-10 구조의 multilayer perceptron(MLP)이며 energy efficient한 동작 방식을 통해 막대한 계산을 요구하는 neural network 연산을 가속한다. 196x128, 128x10 size의 두 SRAM array를 통합하여 MLP를 구성하였고 각각 1st layer, 2nd layer 동작을 수행하도록 설계하였다. Analog voltage로 표현되는 weighted-sum을 입력으로 받아 on-chip Rectified Linear Unit을 출력하도록 하여 ADC-free한 구조를 제안한다. 제안된 SRAM array-based multilayer perceptron은 28nm CMOS 공정에서 설계될 예정이다. Pre-layout simulation 결과 SRAM array의 MAC 동작에서 100 TOPS/W energy efficiency, 52.73 TOPS throughput, 24.91 TOPS/mm2 area efficiency를 달성하였다. |