| IP명 | Embedded RISC-V controlled Spiking Neural Network Processor utilizing Content Addressable Memories for unsupervised learning | ||

|---|---|---|---|

| Category | Analog | Application | Digital PIM |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.1V |

| IP유형 | Hard IP | 동작속도 | 100MHz |

| 검증단계 | Silicon | 참여공정 | SS28-2301 |

| IP개요 | In the proposed hardware, we have shown through simulation that the performance of the new digital SNN algorithm utilizing the TCAMs can outperform state of the art PIMs. In particular the learning performance is highly efficient as well robust as compared to analog MAC computation approaches taken by conventional PIMs. In this research project, we wish to take a step further and develop our architecture to perform unsupervised learning on the MNIST dataset. Furthermore, we also want to develop a controller based on a simple RISC-V (RV32I) ISA. This will enable us to have more flexibility in dealing with autonomous control for individual chips. This will enable the multiple chips to perform a task collectively. Another front that we want to explore is creating a comprehensive test structure to fully characterize our proposed TCAM. We have another version that was created previously on the same 28nm process and we want to revive that architecture by exploiting non-conventional control techniques discovered from the test structure. |

||

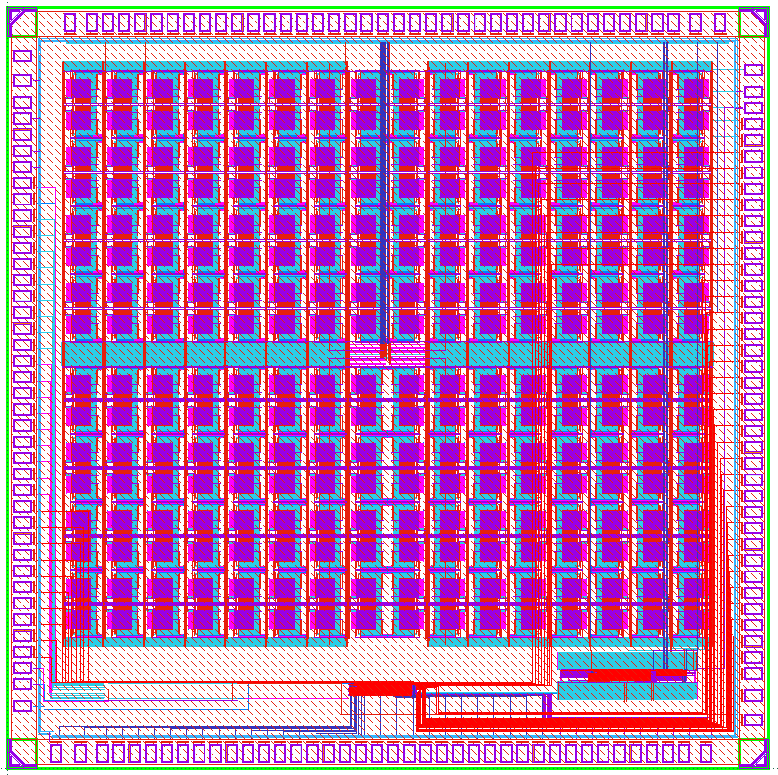

- 레이아웃 사진 -

|

|||