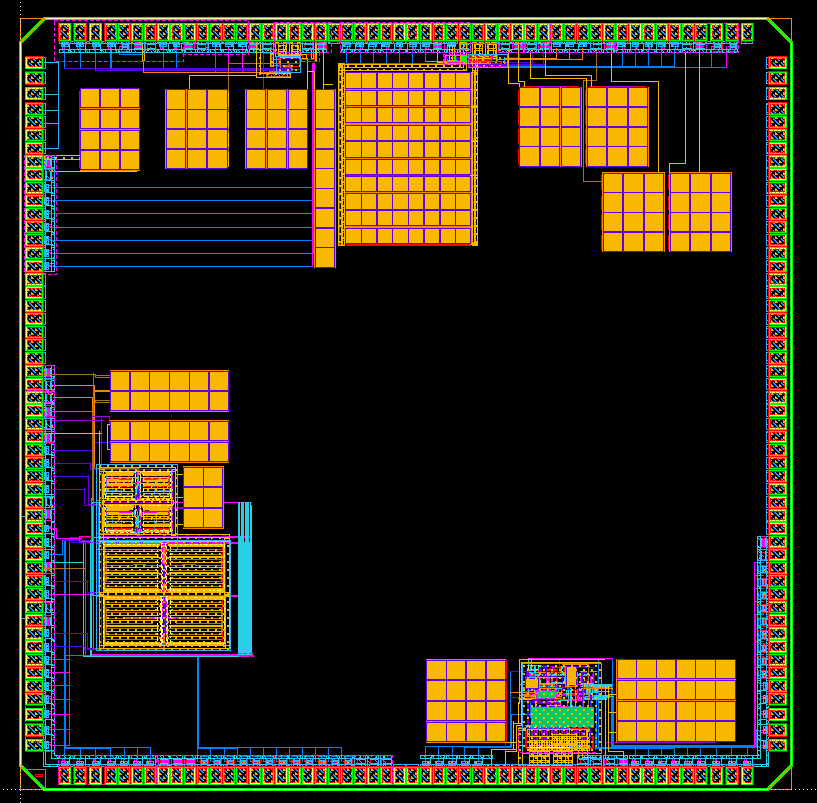

| IP개요 |

This paper proposes a low-area ternary content addressable memory using a don’t care reduction scheme. In Internet Protocol (IP) address, the prefix bits store ‘0’ or ‘1’, and the remaining bits store ‘X’ (don’t care). The conventional ternary content-addressable memory (TCAM) needs a 2N-bit memory for an N-bit IP address, because its TCAM cell uses 2-bit memory to store a data bit (‘0’ or ‘1’) and a don’t care (‘X’) bit. However, the proposed don’t care reduction TCAM (DCR-TCAM) needs a (N+log2N)-bit memory for an N-bit IP address. It also stores N-bit data, but it encodes N-bit ‘X’s into a log2N-bit code, storing the first ‘X’ position. The proposed DCR-TCAM performs the function of ‘X’ in the TCAM from the log2N-bit code by using additional decoders and bypass transistors. A 256×128-bit DCR-TCAM chip was fabricated using a 1.2V 65nm CMOS process. Its area is 0.22mm2, which is only 72% of the conventional TCAM. It expands an effective memory size by applying the data-relocation TCAM scheme [1]. Its energy/bit/search is 0.41fJ at a clock frequency of 330MHz. |