| IP명 | 펄스이동 시간 차 반복회로를 이용한 8비트 2단 시간-디지털 변환기 설계 | ||

|---|---|---|---|

| Category | Analog | Application | ADPLL |

| 실설계면적 | 3.4㎛ X 3.4㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 10MHz |

| 검증단계 | Simulation | 참여공정 | MS180-1904 |

| IP개요 | 본 회로는 자동-지연 부정합 제거 기능을 하는 시간차 반복 회로(Time Difference Repetition circuit)내부에 존재하는 두 펄스 차의 이동을 통해 5ps의 해상도를 갖는 2단 시간-디지털 변환기를 제안한다. 본 회로는 magna 180nm 공정 및 1.8V의 공급전압이 사용되며, 최대동작주파수는 약 700MHz이다. 측정 가능 범위는 약 1.5ns이며, 최소 30 Ms/s의 변환속도를 가진다. | ||

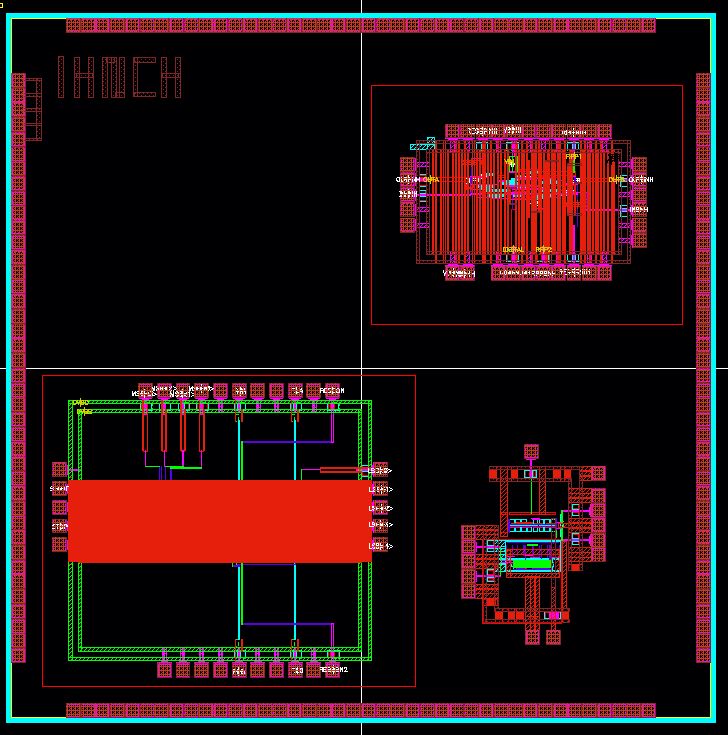

- 레이아웃 사진 -

|

|||