| IP명 | PLL with TRNG | ||

|---|---|---|---|

| Category | Analog | Application | 유선통신 |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 14GHz |

| 검증단계 | Silicon | 참여공정 | SS028-1901 |

| IP개요 | 본 설계에서는 True Random Number Generator을 이용한 Spur Reduction Technique을 포함하는 Phase Locked Loop 설계회로를 제안한다. 설계 공정은 Samsung 28nm 공정을 이용하였으며 공급 전압은 1.2V이고, 회로 타입은 Analog & Mixed-Signal 이다. | ||

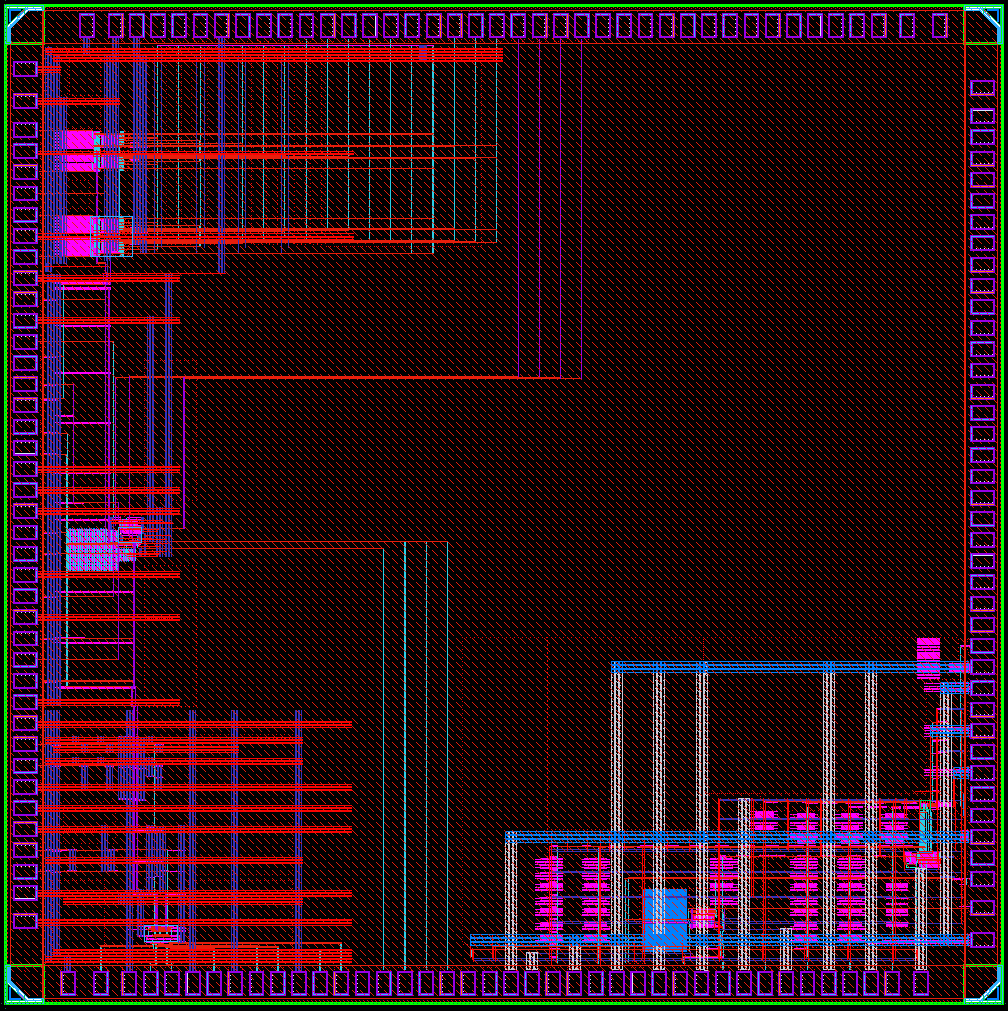

- 레이아웃 사진 -

|

|||