| IP명 | 12-b 5-MS/s RC-Hybrid DAC based Multi-channel SAR ADC with Conversion Time Modification Logic | ||

|---|---|---|---|

| Category | Analog | Application | Data Converter |

| 실설계면적 | 4㎛ X 2㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 250MHz |

| 검증단계 | Silicon | 참여공정 | SS028-2201 |

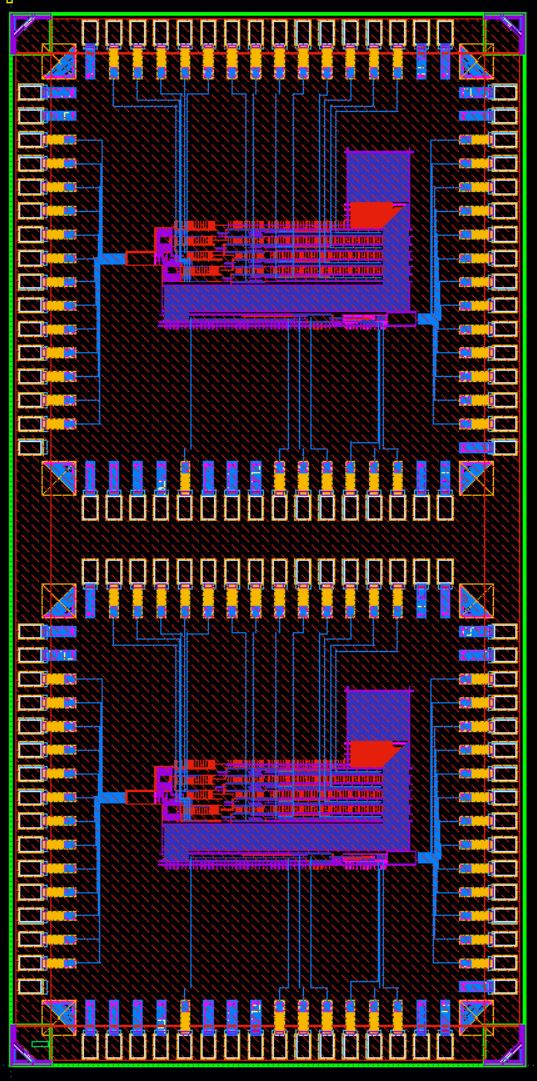

| IP개요 | In this work, a two-step SAR ADC is proposed applicable to high-speed CIS systems. The design techniques are as follows. Firstly, to reduce the area, we use resistor DAC (RDAC) and capacitor DAC (CDAC) separately, and the resistor DAC applies a certain layout technique, called cross-connected layout method, to increase device matching. Secondly, to resolve settling time issue by using resistor, bit-cycling time control logic and LSB correction logic have been implemented for enhancing sampling speed of the ADC. |

||

- 레이아웃 사진 -

|

|||