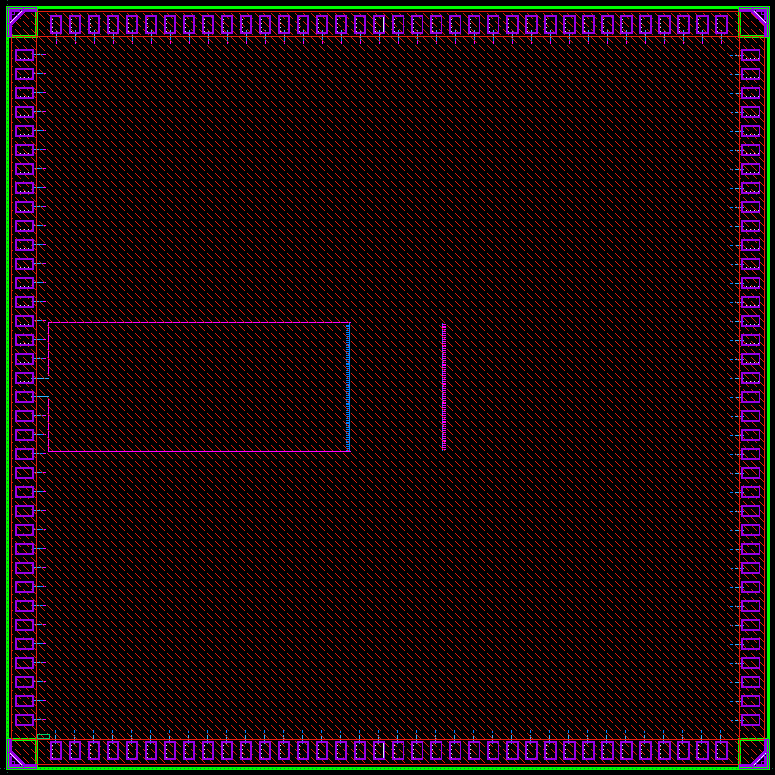

| IP개요 |

This proposal presents a 0.6 V 6 MS/s 10-bit SAR ADC with a double rail-to-rail input range, designed for extended applica-tion use, including compute-in-memory systems. The proposed ADC achieves area efficiency by requiring only two additional se-ries-connected capacitors and a differential-difference comparator for double rail-to-rail operation. Furthermore, the set-and-down op-eration significantly reduces the input-referred noise of the compar-ator, achieving over ten times lower noise compared to complemen-tary switching. To enhance accuracy, a hybrid capacitor DAC archi-tecture, combining metal-insulator-metal and metal-oxide-metal ca-pacitors, is employed to minimize gain error. |