| IP명 | Data and Power Efficient ReLU-Based Transformer Accelerator Leveraging Activation Sparsity | ||

|---|---|---|---|

| Category | Digital | Application | NPU |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 100MHz |

| 검증단계 | Silicon | 참여공정 | SS28-2501 |

| IP개요 | 본 설계에서는 효율적인 AI 연산을 위해 활성화 희소성을 활용할 수 있는 트랜스포머 가속기를 설계한다. 활성화 함수의 출력 값을 예측하는 방법을 통해 비트 단위로 불필요한 연산을 건너뛰고, 메모리를 고려한 효율적인 데이터 이동을 가능하게 하는 설계이다. ReLU 기반의 어텐션의 활성화 함수 변환을 통해 트랜스포머 모든 레이어에서 희소성을 활용할 수 있도록 하고, 비트 분리 가능한 곱셈기와 동적 범위 디코더를 통해 활성화 함수를 고성능, 저전력, 저비용으로 처리하는 방법을 제시한다. 또한, AI 추론 시스템에서 가장 많은 전력을 소모하는 DRAM의 데이터 접근을 최소화하기 위해 subarray 병렬화를 위한 DRAM 인터페이스를 포함한다. |

||

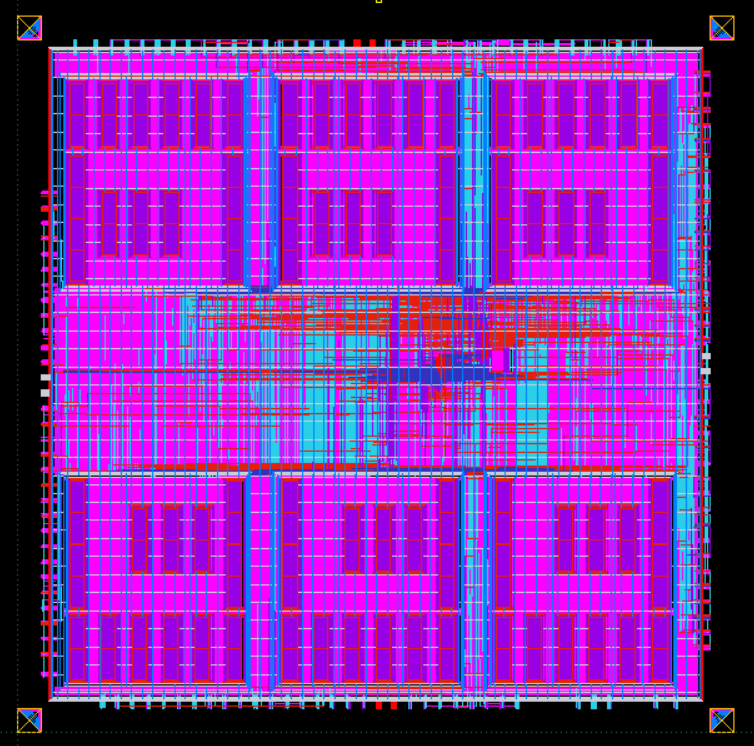

- 레이아웃 사진 -

|

|||