| IP개요 |

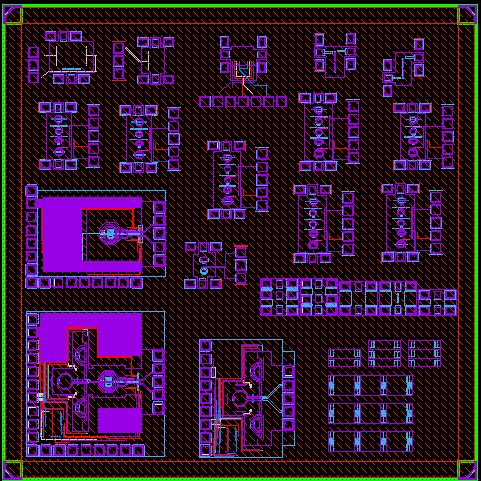

본 제안에서는 D-band (110 – 170 GHz) phased-array system 구현을 위한 광대역 variable-gain amplifier (VGA)를 제안한다. 기존에 VGA 구현을 위해 사용되던 current-steering 구조와 비교하여 구조적으로 설계에 유리한 active cross-coupling neutralization (ACCN) 구조의 VGA cell을 사용하였다. 또한 VGA cell 입력 네트워크로 3단 트랜스포머 구조를 제안하였다. 해당 구조를 사용하면 D-band와 같은 높은 주파수에서 dc-block capacitor 사용을 최소화할 뿐만 아니라 더 적은 면적으로 VGA cell 구현이 가능하다. 설계된 D-band VGA는 총 4단으로 구성되어 있으며, 2번째 단에 제안된 3단 트랜스포머를 이용한 ACCN VGA cell이 위치한다. 입력은 발룬은 common-mode를 억제하기 위하여 첫 번째 코일의 center-tap을 그라운드에 연결한 구조를 사용하여 전체 이득을 향상시켰다. 131 GHz에서 최대 이득은 16.5 dB이고, 이득 조정 범위는 12.3 dB를 가진다. 3-dB 대역폭은 122.6 GHz부터 140.4 GHz까지의 넓은 범위를 보였다. 회로는 1V 공급 전원에서 최대 41.2 mW의 전력을 소모한다. |