| IP명 | Energy-Efficient Transformer with Dynamic Sparsity Attention Using Large-Scale Configurable Winner-Take-All Circuit | ||

|---|---|---|---|

| Category | Analog | Application | AI |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 100MHz |

| 검증단계 | Silicon | 참여공정 | SS28-2501 |

| IP개요 | 본 설계계획서는 large-scale configuration이 가능한 winner-take-all (WTA) 회로를 활용하여 dynamic sparsity attention을 구현함으로써 accuracy와 energy consumption이 개선된 transformer 구조를 제안한다. 제안된 dynamic sparsity attention은 KNN 기반 clustering을 통해 query (Q)와 key(K)를 분류한 후 look-up table (LUT)을 활용하여 Q와 K의 중요도를 예측한다. 이 때 Q와 K의 dimension이 크기 때문에 높은 accuracy를 구현하기 위해선 충분한 개수의 clustering이 필요하며, 이를 위해 본 설계에서는 128개의 clustering을 구현하여 transformer 모델의 정확도를 향상시켰다. 또한, 이에 사용되는 WTA는 clustering의 개수에 비례해서 전력소모 및 면적이 증가하는 경향을 보이는데, 이를 해결하기 위해 본 연구에서는 parallel 구조와 inhibition signal을 적용한 WTA를 설계하여 large-scale 환경에서도 energy-efficient하고 compact한 면적을 달성하였고, 이를 통해 energy-efficiency한 dynamic sparsity attention 시스템을 개발하였다. 제안된 WTA는 power consumption 및 area를 기존 회로 대비 각각 최대 85.1% 및 86.8%까지 감소하였고 16×640 SRAM macro 4개와 제안된 WTA로 이루어진 dynamic sparsity attention 시스템은 28nm CMOS 공정에서 설계될 예정이다. |

||

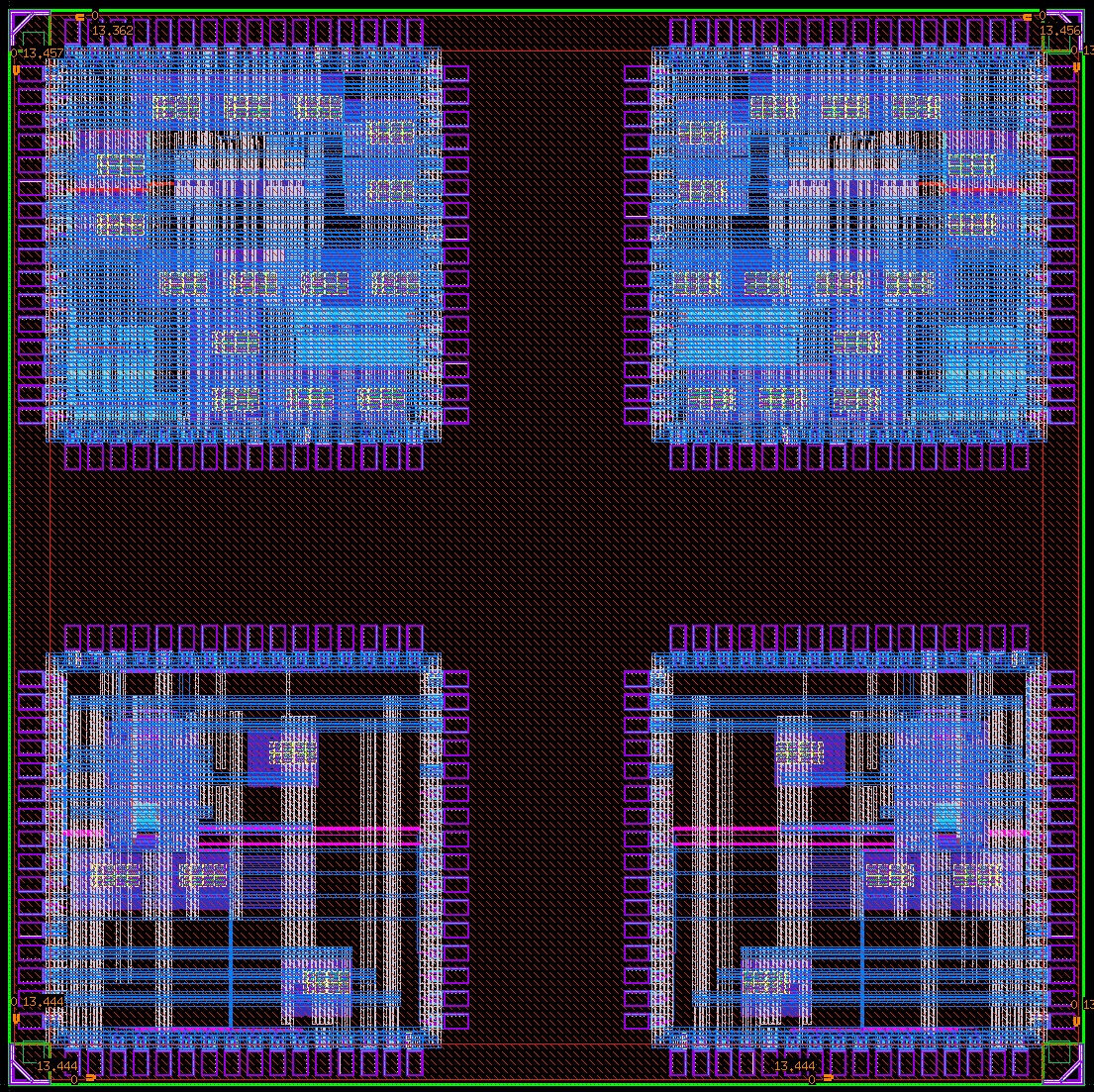

- 레이아웃 사진 -

|

|||