| IP개요 |

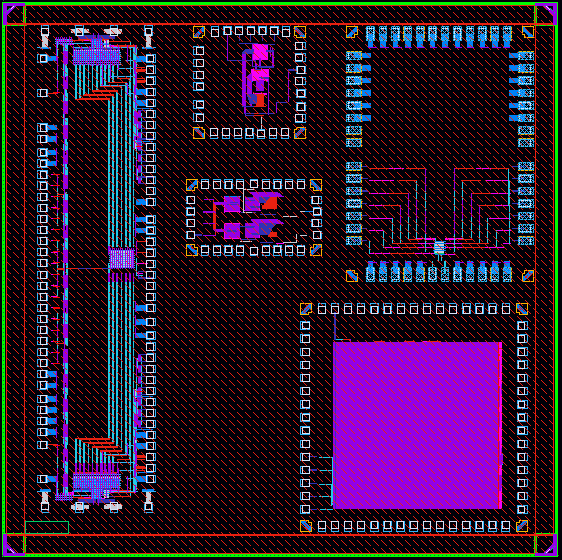

심층신경망 또는 합성곱 신경망 등의 인공지능의 급속한 발전으로 인한 매개변수 및 데이터 양의 증가는 전통적인 컴퓨팅 시스템 구조인 폰 노이만(Von-Neumann) 구조에 심각한 병목현상을 야기한다. 과도한 데이터 전달로 인한 에너지 소모 및 지연시간 증가 등의 문제점들을 해결하기 위해서, 최근 메모리 내에서 연산을 수행하는 구조인 Processing-In-Memory (PIM)에 대한 연구가 활발히 진행되고 있다. 본 MPW에서는 이진 심층 신경망을 타겟 네트워크로 하여 메모리 및 연산 효율을 높이고, 최소한의 사이즈로 학계 최고 수준의 정확도에 비견할 만한 PIM 회로를 설계하는 것을 목적으로 한다. 또한 인공지능 회로에서 주요 연산인 내적 연산뿐 아니라, Arithmetic Logic Unit (ALU) Mode를 지원하여 logic compatible한 PIM 하드웨어 매크로를 설계하고자 한다. 마지막으로, PVT variation이나 Analog to Digital (ADC)의 양자화로 인한 Analog 회로들의 비이상성을 모델 학습에 반영하는 Analog nonidealityaware training을 통하여 제작된 하드웨어의 비이상성으로 인한 정확도 저하를 최소화하는 기법을 적용하여 하드웨어 의존성을 낮추는 연구를 진행하고자 한다. |