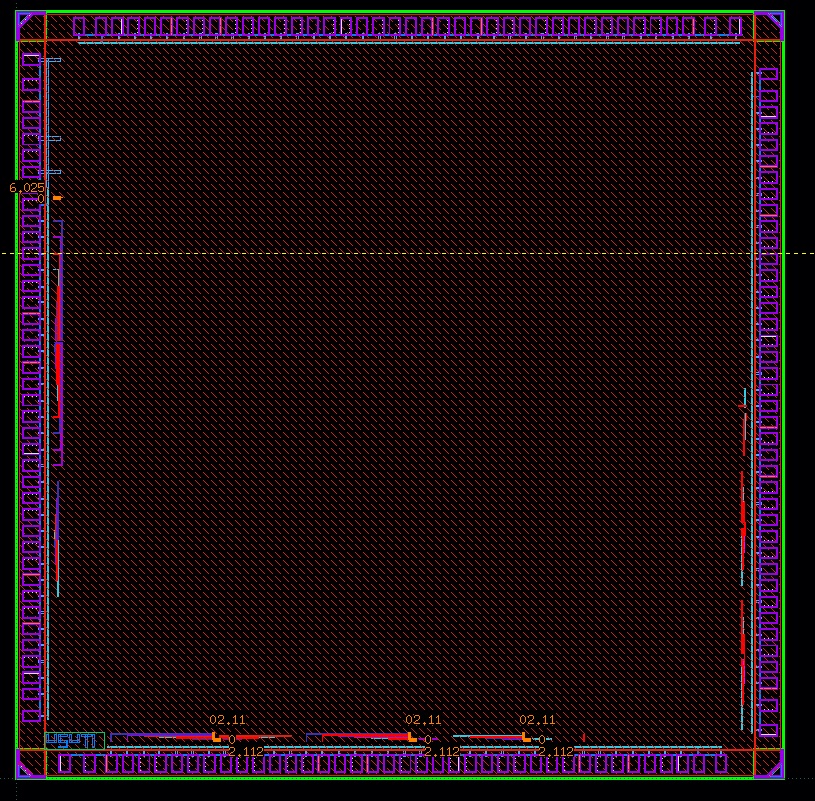

| IP개요 |

In this proposal, the novel low-power sense-amplifier-based flip-flop using floating node elimination technique is proposed for MPW (Samsung 28 nm LPP process) application. As the technology of very large-scale integrated circuits (VLSI) developed, the requirements of high speed, small area, low power, and high yield are increasing. The flip-flop (FF) is a key element as most modern microprocessors operate under the synchronous pipeline structure. Under this condition, the proposed sense amplifier-based flip-flop can achieve high performance reconfiguring two transistors which can conditionally turn on a shortening device without undesired charge and with low voltage resulting in high operation yield, lower power consumption and small area. The Spectre (Cadence) transient simulation result with Samsung 28 nm LPP process shows the function verification of the proposed circuit. |