| IP명 | Two-step ADC with Self-Successive Doubling Algorithm for High-Speed CIS | ||

|---|---|---|---|

| Category | Analog | Application | IMAGE SENSOR |

| 실설계면적 | 5㎛ X 3.3㎛ | 공급 전압 | 2.8/1.8V |

| IP유형 | Hard IP | 동작속도 | 50MHz |

| 검증단계 | Silicon | 참여공정 | HM-2501 |

| IP개요 | 본 발명은 자기 연속 배가(SSD, Self-Successive Doubling) 알고리즘을 적용한 투스텝 아날로그-디지털 컨버터(ADC)를 사용하는 고속 CMOS 이미지 센서(CIS)를 제안한다. 제안된 리드아웃 회로는 SAR(연속 근사 레지스터) ADC를 활용하여 고속 CIS를 구현하며, SSD 회로를 도입함으로써 SAR ADC의 면적 요구 사항을 해결한다. SSD 회로는 기존의 아날로그 상관 이중 샘플링(CDS) 회로와 유사한 구조를 가지고 있어, CDS와 ADC 연산을 동시에 수행할 수 있다. 이로 인해 SAR ADC에 필요한 커패시터 면적이 크게 줄어들며, 12비트 해상도 기준으로 약 96.8%의 면적 절감 효과를 달성한다. 제안된 회로는 180nm 공정을 통해 제작되었으며, 전체 소비 전력은 7.54mW, 프레임 속도는 1190fps이다. | ||

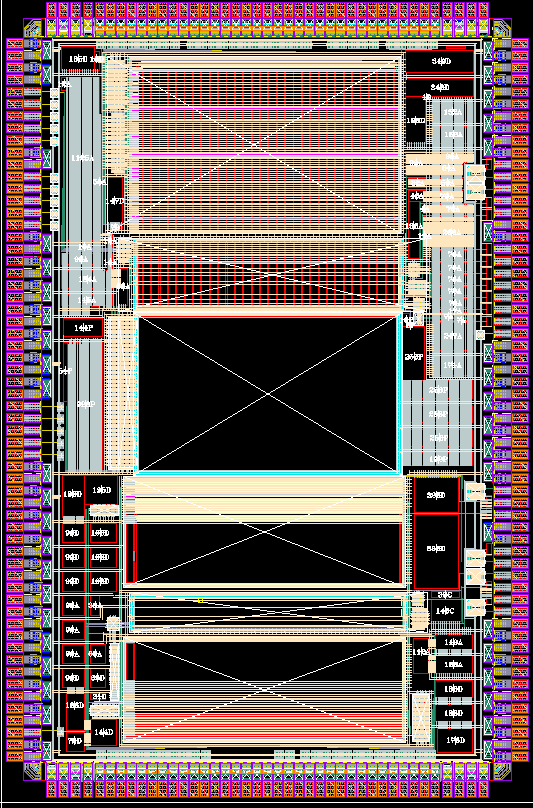

- 레이아웃 사진 -

|

|||