| IP명 | A Single-Channel Synchronous SAR ADC using Successive-Approximation-based Metastability Resolving Technique | ||

|---|---|---|---|

| Category | Mixed | Application | Analog to Digital Converter |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | 동작속도 | 1GHz | |

| 검증단계 | Silicon | 참여공정 | SF028-2501 |

| IP개요 | This proposal presents a single-channel successiveapproximation-register (SAR) analog-to-digital converter (ADC) with metastability resolving technique. In SAR ADC, metastability of comparator makes huge error code, which degrades the dynamic performance of ADC. Therefore, the comparator generally accounts for relatively large proportion of total power consumption in highspeed design. The proposed technique prevents the error code by utilizing the property of successive-approximation code generation and positive feedback of memory cell with cross-coupled transistors. It maximizes the operation speed of SAR ADC and relaxes comparator design requirement with relatively small increase in digital logic, resulting in good trade-off between speed and power consumption of ADC operation. |

||

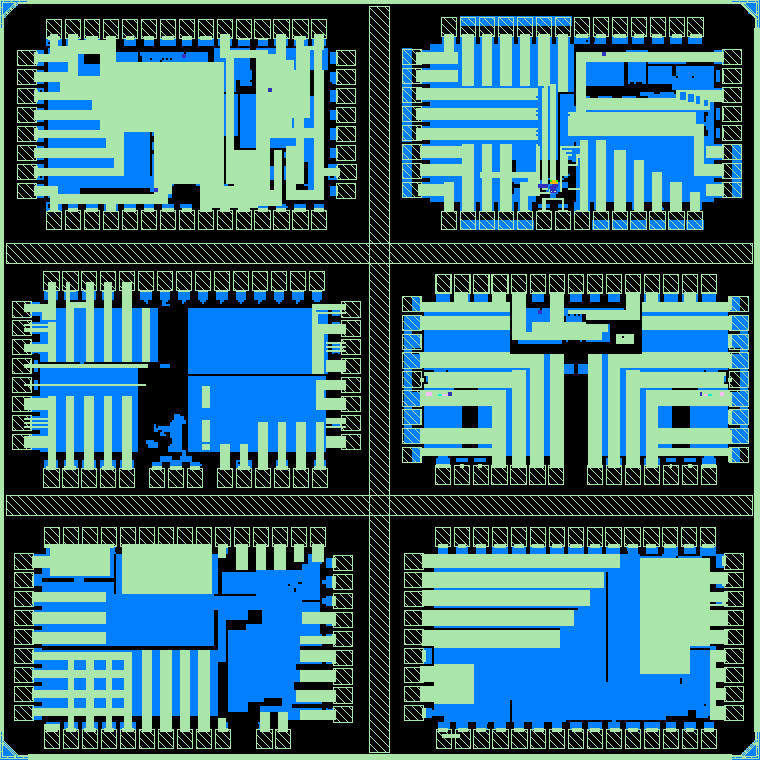

- 레이아웃 사진 -

|

|||