| IP개요 |

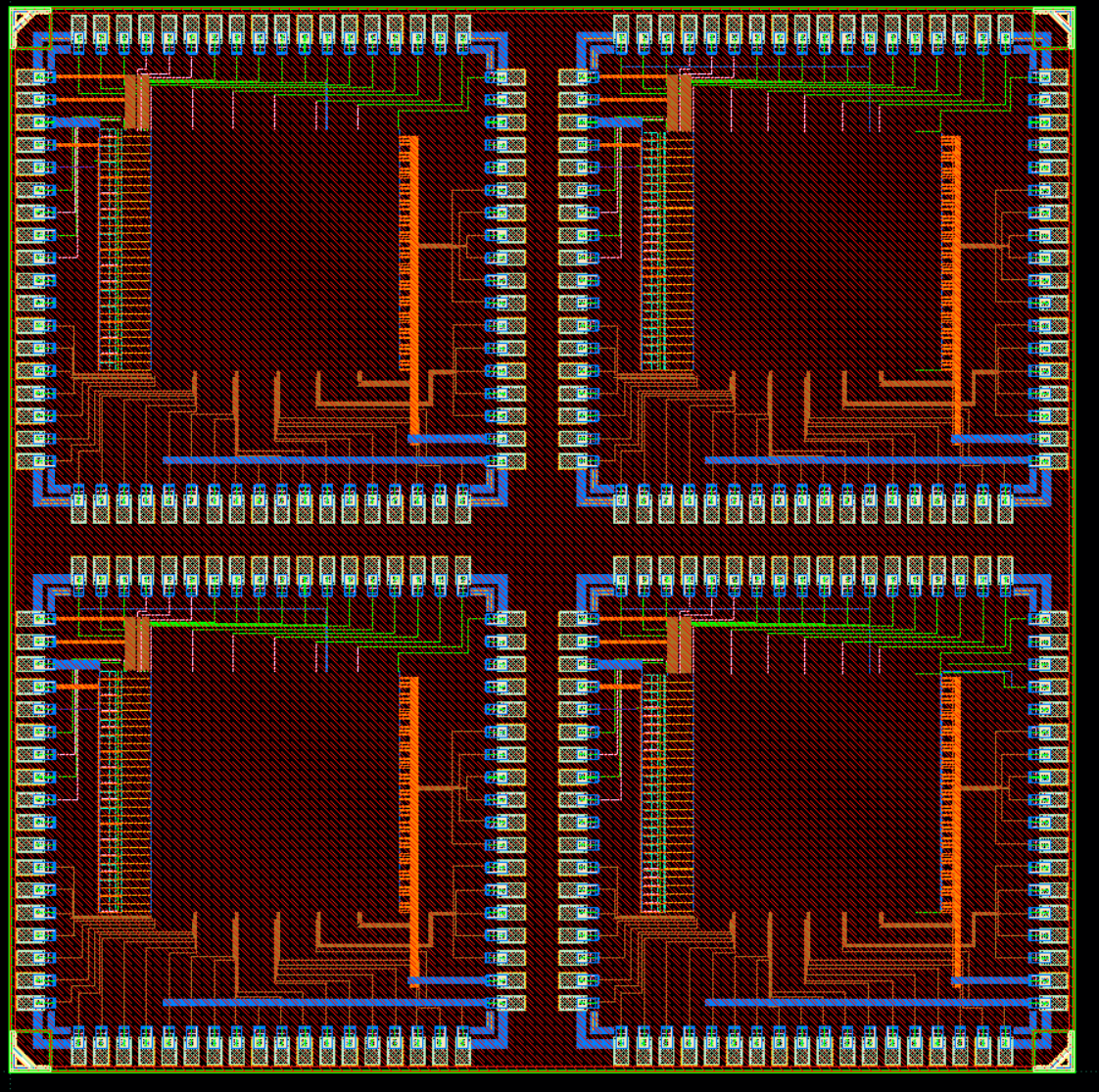

본 희망공정 MPW 설계 지원서는 저전압 환경에서 high power-supply-rejection (PSR)을 가지는 analog low-dropout (LDO)회로를 제안한다. 1V미만의 낮은 전원 전압에서 high PSR을 가지기 위해, multi-stage로 구성하여 높은 loop gain을 가지는 회로가 필요하다. 또한 높은 전력 효율을 위해 작은 drop out voltage를 가지면서도 높은 loop gain을 유지하는 방법을 사용한다. 이를 달성하기 위해 loop내에 error amplifier가 없는 Flipped-Voltage-Follower (FVF) 기반의 LDO 회로 구조를 변형하여 낮은 전원전압에서 높은 loop gain을 가지는 회로를 만들었다. 제안하는 회로는 SF 28nm 공정을 사용하여 설계하였고, analog 회로로 설계한다. LDO 회로에서는 0.6V 전원전압을 사용하며, 50mV의 drop out voltage를 가지며 10MHz에서 -20dB이상의 PSR을 목표로 설계할 예정이다. |