| IP명 | A Single-Ended Transmitter with Asymmetric Crosstalk Cancellation for Data Bus Inversion in Low Power Memory Interfaces | ||

|---|---|---|---|

| Category | Mixed | Application | memory interfaces |

| 실설계면적 | 2㎛ X 2㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 9GbpsHz |

| 검증단계 | Silicon | 참여공정 | HM-2503 |

| IP개요 | The proposed single-ended transmitter for data bus inversion (DBI) in low-power memory interfaces utilizes asymmetric crosstalk cancellation (AXTC). Unlike conventional FIR-based crosstalk cancellation (XTC) methods, which symmetrically apply amplitude-based XTC regardless of transition direction, thereby incurring static power consumption during consecutive logic-0 (CLZ) transmission, the proposed transmitter eliminates crosstalk through asymmetric slew-rate control applied only during logic-1 to logic-0 transitions, without incurring static power. Additionally, a phase equalization (PEQ) technique combined with AXTC is integrated to effectively compensate for inter symbol interference (ISI) while preserving energy efficiency under DBI-encoded signaling. |

||

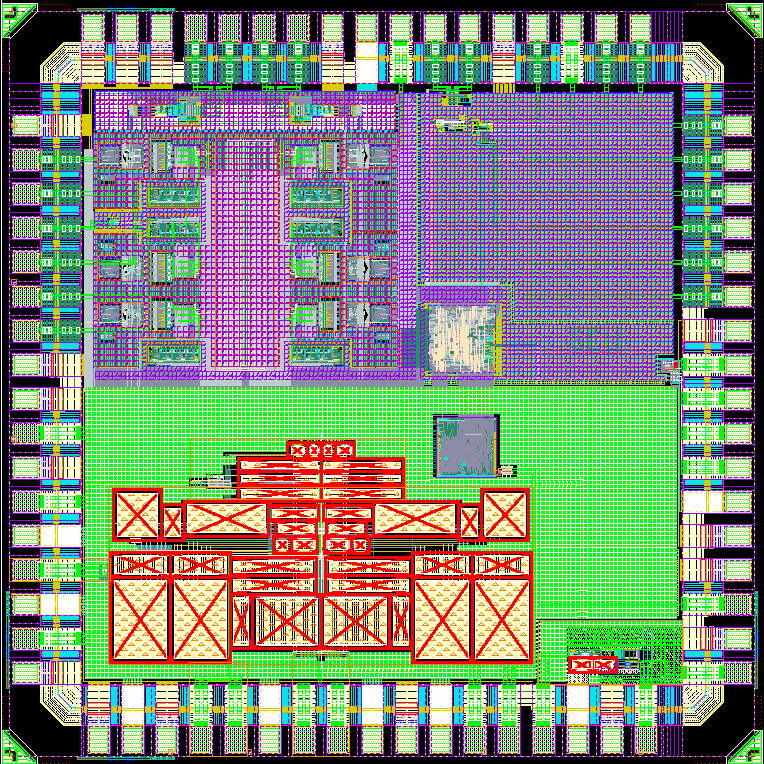

- 레이아웃 사진 -

|

|||