| IP명 | Low-Noise Transimpedance Amplifier Using Multiple Compensation Techniques for Nanopore Sensing | ||

|---|---|---|---|

| Category | Analog | Application | Biomedical Engineering |

| 실설계면적 | 3.5㎛ X 3.5㎛ | 공급 전압 | 5V |

| IP유형 | Hard IP | 동작속도 | 100KHz |

| 검증단계 | Simulation | 참여공정 | SB130-2502 |

| IP개요 | In this design proposal, we present a low-noise transimpedance amplifier (TIA) structure for nanopore applications. The proposed system includes a pseudo-resistor, a negative capacitance generator (NCG), and a chopper stabilization technique to improve overall noise performance. Low-frequency noise is reduced using the chopper stabilization method, while high- frequency noise—mainly caused by parasitic capacitance in the nanopore environment—is reduced by the NCG. Circuit-level analysis shows that the design can effectively minimize noise. In addition, simulation results suggest that the proposed system performs well in reducing noise. Based on these results, we plan to move forward with chip fabrication using the SB 130nm BCDMOS process. |

||

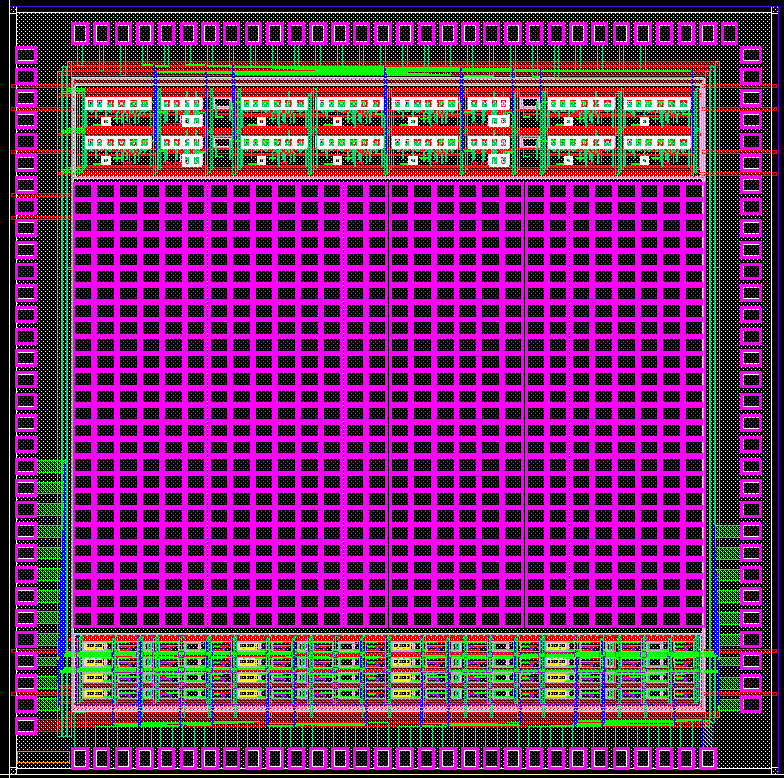

- 레이아웃 사진 -

|

|||