| IP명 | A Full Boolean Logic Supportable 4T2C eDRAM-Based Digital CIM with Toggle-Reduced Digital Adders for Energy- Efficient Computation | ||

|---|---|---|---|

| Category | Analog | Application | Memory |

| 실설계면적 | 2㎛ X 4㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 250Hz |

| 검증단계 | Silicon | 참여공정 | SS028-2502 |

| IP개요 | 기존 CIM processor들은 cell density와 지원 가능한 연산 범위 사이의 trade off를 겪고 있다. 이로 인해 cell density가 현저히 감소하는 문제가 있고 대량의 병렬 연산으로 인해 발생하는 adder tree의 높은 전력 소모 역시 중요한 문제로 떠오르고 있다. 따라서 본 연구에서 full boolean logic supportable DCIM macro를 제안하여 bit cell density를 높이면서 연산 유연성을 확보한다. | ||

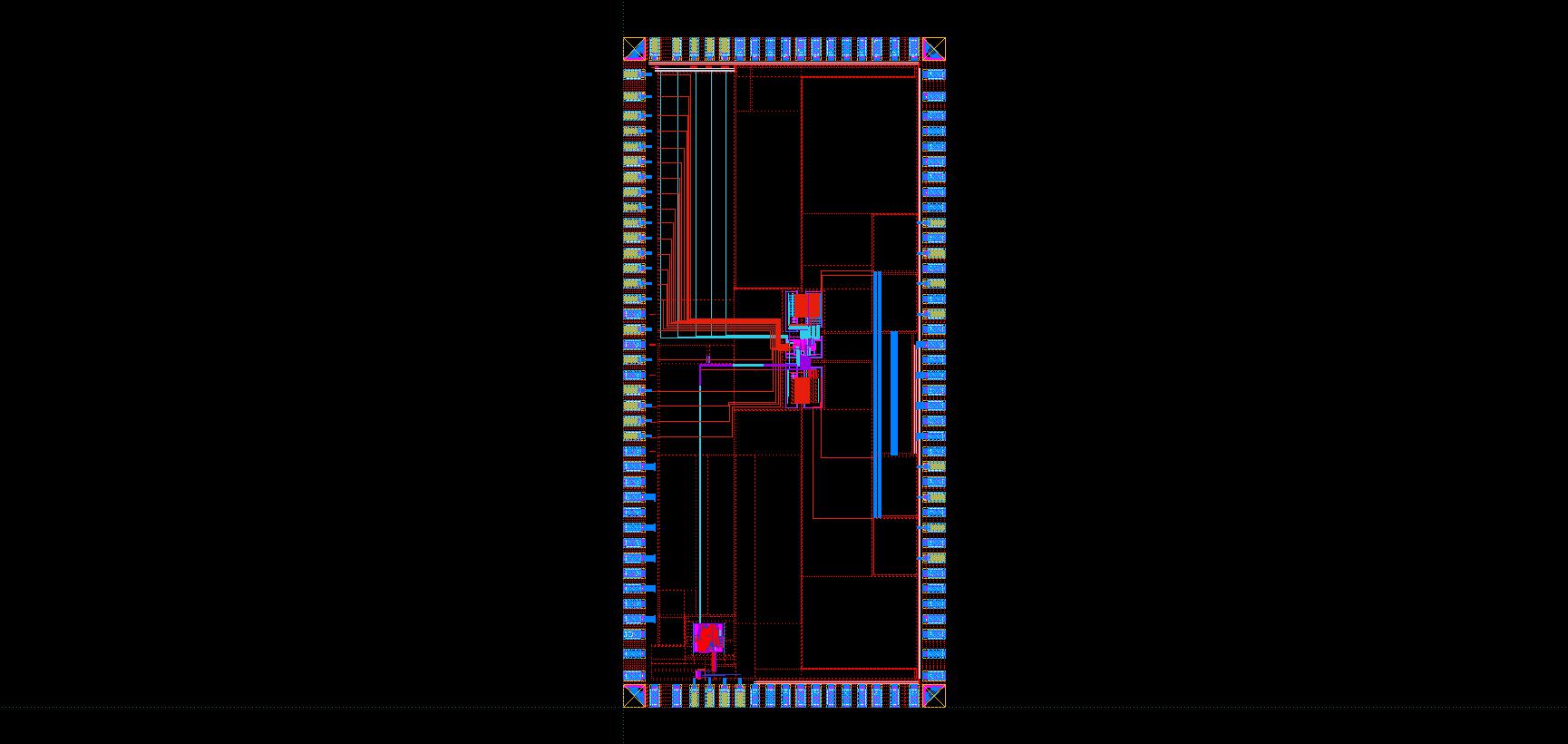

- 레이아웃 사진 -

|

|||