| IP명 | A 56Gb/s Power-Efficient Clock and Data Recovery Circuit with Dynamic Slicer Control Scheme | ||

|---|---|---|---|

| Category | Analog | Application | 통신회로 |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 56GHz |

| 검증단계 | Silicon | 참여공정 | SS028-2502 |

| IP개요 | 본 연구에서는 56-Gb/s 속도의 PAM-4 quarter-rate CDR을 제안하며, 이는 고속 동작과 동시에 전력 효율을 향상시키는 구조를 갖는다. 전력 소모 및 정밀도 요구를 해결하기 위해, 본 논문은 동적 슬라이서 제어(dynamic slicer control, DSC) 기법이 적용된 새로운 전력 효율적 위상 검출기(Power-Efficient phase detector, PEPD) 구조를 제안한다. | ||

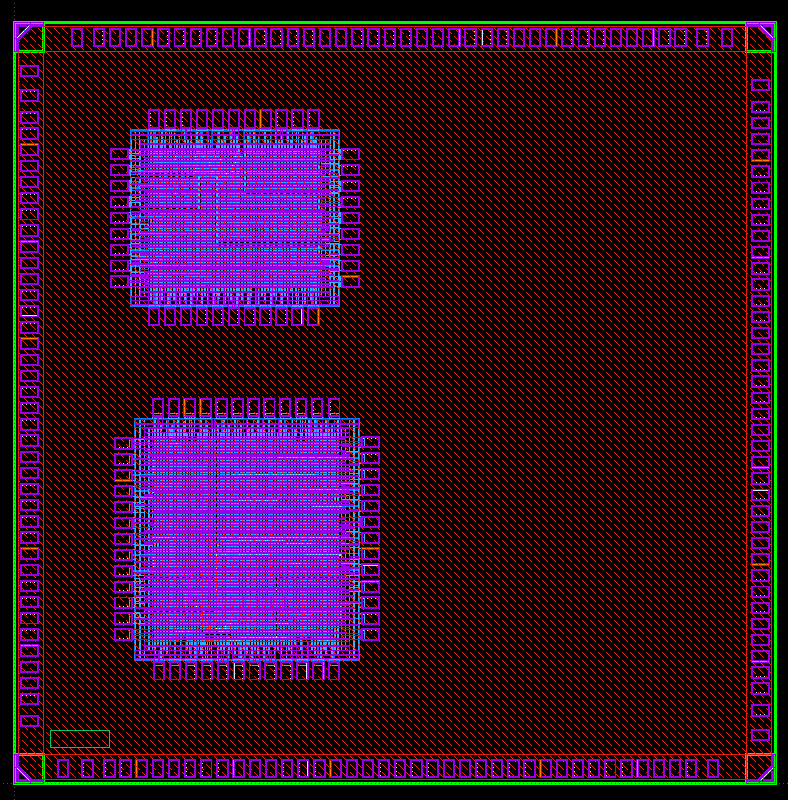

- 레이아웃 사진 -

|

|||