| IP명 | A 4 GS/s Time-interleaved Two-step SAR-Flash Hybrid ADC With A Digital Background Calibration Engine | ||

|---|---|---|---|

| Category | Mixed | Application | Analog to Digital Converter |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.0V |

| IP유형 | Hard IP | 동작속도 | 4GHz |

| 검증단계 | Silicon | 참여공정 | SS028-2502 |

| IP개요 | 본 설계는 채널 간 부정합 보정 엔진(Calibration Engine)이 내장된 고속 저전력 Time-Interleaved (TI) Analog-to-Digital Converter (ADC)에 관한 것으로, 다채널 구조를 사용하는 TI ADC의 근본적인 한계인 채널 간 불일치(offset, gain, time-skew mismatch)로 인한 성능 저하를 최소화하고, 고속 동작과 저전력을 동시에 달성하는 것을 주요 설계 목표로 한다. 이를 위하여, 각 TI 채널에 사용되는 sub-ADC로는 전력 효율이 개선된 two-step 구조의 SAR-Flash 하이브리드 ADC를 제안하였으며, 해당 구조는 SAR 방식의 에너지 효율성과 Flash 구조의 속도 특성을 융합하여 고속 저전력 특성을 동시에 확보할 수 있도록 설계되었다. | ||

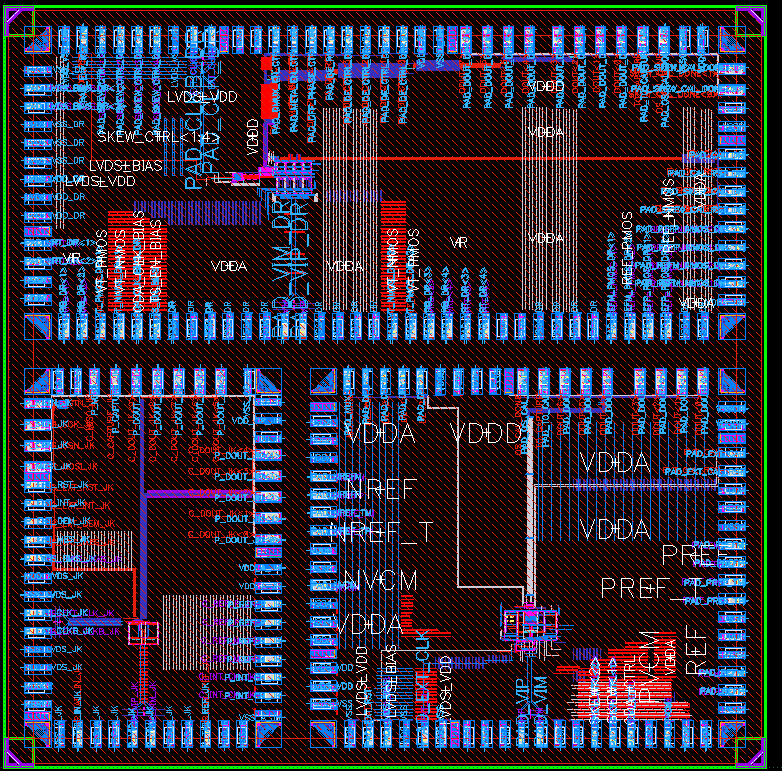

- 레이아웃 사진 -

|

|||