| IP명 | Energy-Efficient Capacitively-Driven Link with 1-Bit Edge Modulation and DBI-AC-Based XTC for ISI and Crosstalk Mitigation in Next-Generation HBM Interfaces | ||

|---|---|---|---|

| Category | Mixed | Application | High Speed Link |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 10GHz |

| 검증단계 | Silicon | 참여공정 | SS028-2502 |

| IP개요 | Growing demands of LLM and ML workloads have intensified the need for high-bandwidth energy-efficient memory interfaces. HBM, interconnected through silicon interposers, presents RC-dominant channel characteristics that challenge conventional signaling approaches. In this MPW proposal, we propose a capacitive-driven link architecture tailored for HBM interfaces, leveraging its inherent energy efficiency and robustness to supply noise. To address the increased inter-symbol interference (ISI) and data-dependent jitter (DDJ) increased by DBI-AC encoding in HBM, we employ a low-overhead, pattern-dependent edge-shift technique. This not only mitigates signal integrity (SI) degradation but also reduces simultaneous switching noise (SSN) and power-supply-induced jitter (PSIJ). Additionally, the DBI-AC scheme is modified to limit the maximum number of transitions to two within each 4-bit group, thereby eliminating worst-transition patterns and improving crosstalk-induced jitter (CIJ). To enable PAM-4 signaling with this enhanced DBI-AC, the novel silicon interposer channel architecture is proposed. Operating above 15 Gb/s with energy consumption below 0.1 pJ/bit, the proposed link addresses critical SI/PI challenges and paves the way for scalable, low-power memory interfaces in future AI and HPC systems. |

||

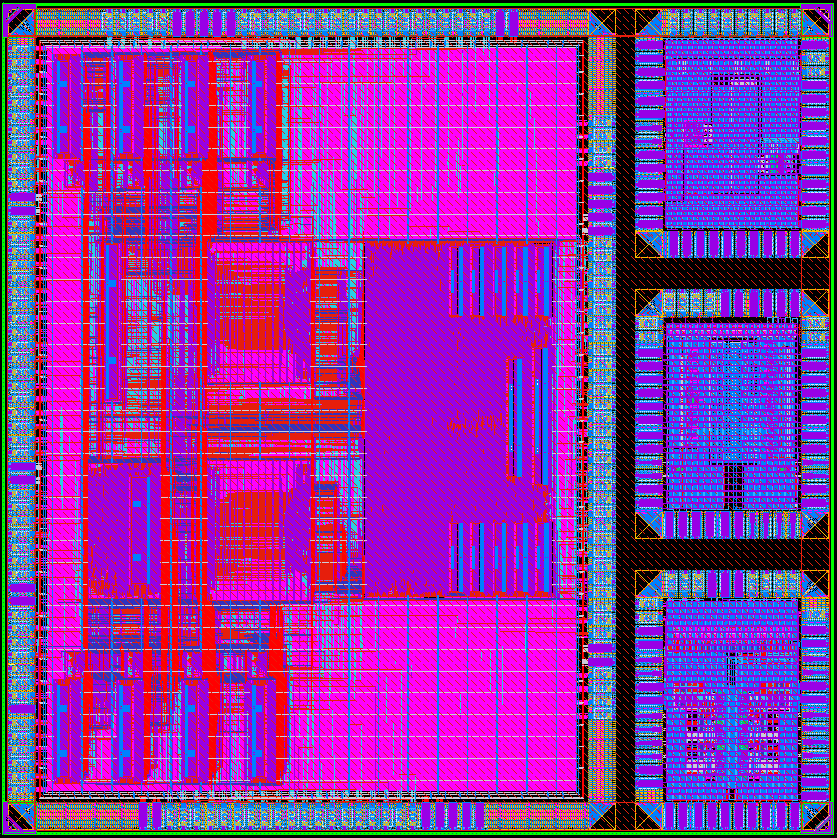

- 레이아웃 사진 -

|

|||