| IP명 | 저전력·고효율 eDRAM PIM용 FP16 PE 설계 | ||

|---|---|---|---|

| Category | Mixed | Application | TTS,SV,PIM |

| 실설계면적 | 1㎛ X 1㎛ | 공급 전압 | 1.8V |

| IP유형 | Soft IP | 동작속도 | 100Hz |

| 검증단계 | FPGA | 참여공정 | SF028-2502 |

| IP개요 | 본 IP는 eDRAM 기반 PIM 아키텍처에서 동작하는 FP16 기반 Processing Element로, 저전력 AI 추론 가속을 목적으로 개발되었다. 기존 von Neumann 구조에서는 연산 유닛과 메모리 간 데이터 이동이 큰 전력 손실과 병목을 유발하므로, 메모리 인접 영역에서 직접 연산을 수행하는 PIM 방식이 차세대 AI 반도체의 핵심 기술로 주목받고 있다. 본 IP는 이러한 PIM 구조에 적합한 FP16 연산 유닛을 제공한다. 설계된 PE는 FP16 multiplier, FP16 adder, 그리고 MAC datapath를 포함하며, exponent 비교 및 정렬, mantissa 처리, normalization, rounding/precision loss detection, exception flag generation 기능을 수행한다. 이를 통해 AI inference에 필요한 실수 연산을 비교적 높은 정확도로 지원하면서도, 하드웨어 복잡도와 소비 전력을 낮출 수 있다. 또한 eDRAM memory array와 연계 가능한 구조를 고려하여 설계함으로써, 메모리 접근 오버헤드를 줄이고 전체 시스템의 처리 효율을 향상시킨다. 본 IP는 edge AI, TTS, 소형 언어모델(sLLM), 스마트 시스템용 추론 가속기 등에 활용 가능하며, 향후 다수의 PE를 병렬 배치한 PIM accelerator로 확장 가능한 기반 IP로 활용될 수 있다. |

||

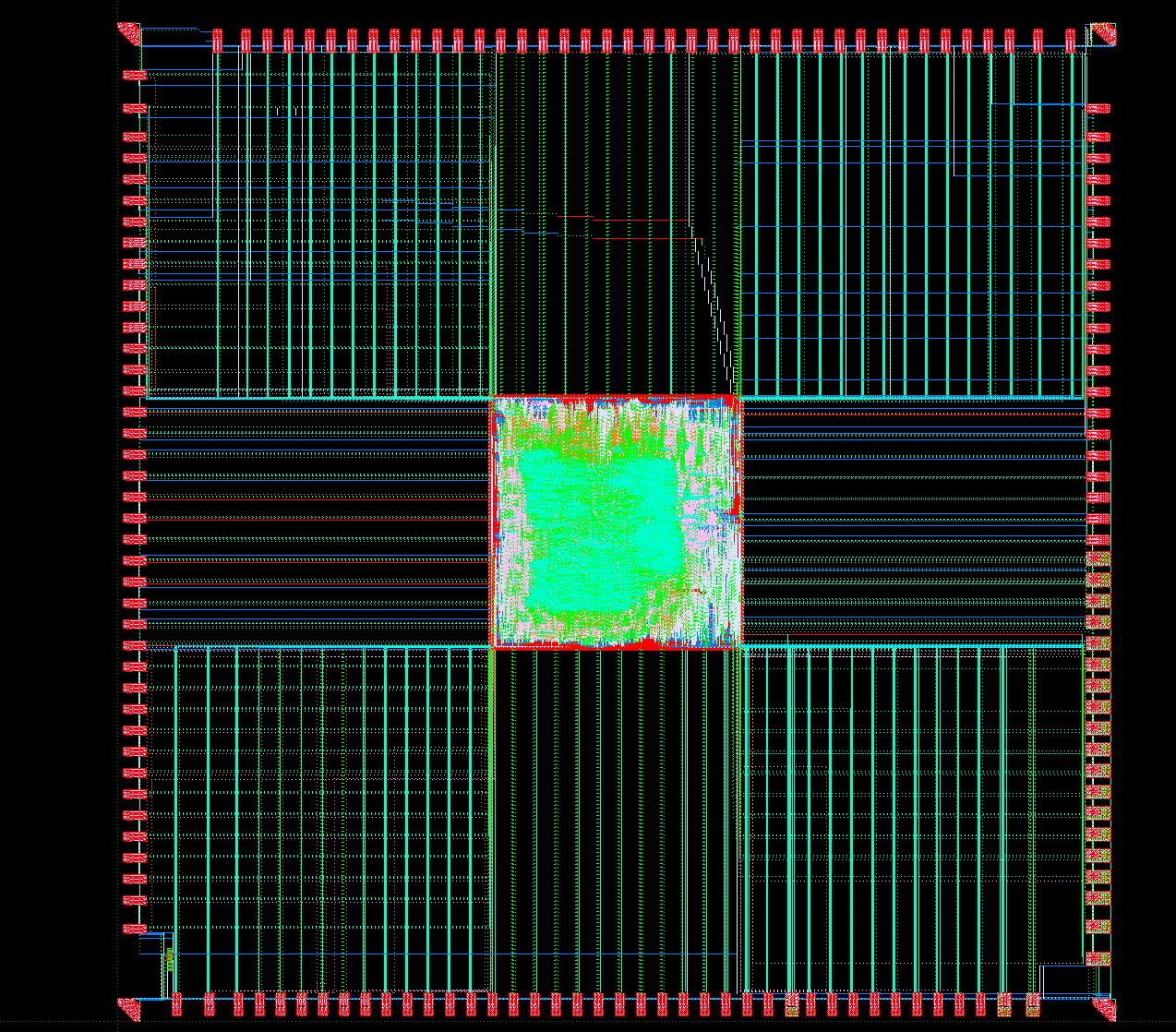

- 레이아웃 사진 -

|

|||