| IP명 | High-Speed Clock and Data Recovery Using Injection-Locked Oscillator and Phase Interpolator | ||

|---|---|---|---|

| Category | Mixed | Application | High Speed Interface |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 14GHz |

| 검증단계 | Silicon | 참여공정 | SF028-2502 |

| IP개요 | This IP is a high-performance Clock and Data Recovery (CDR) circuit designed for high-speed serial data communication. It employs a dual-stage architecture that separates frequency and phase acquisition to optimize stability and performance. The system features an all-digital control loop, utilizing an Injection-Locked Ring Oscillator (ILRO) for robust frequency generation and a high-resolution Phase Interpolator (PI) for precise data tracking | ||

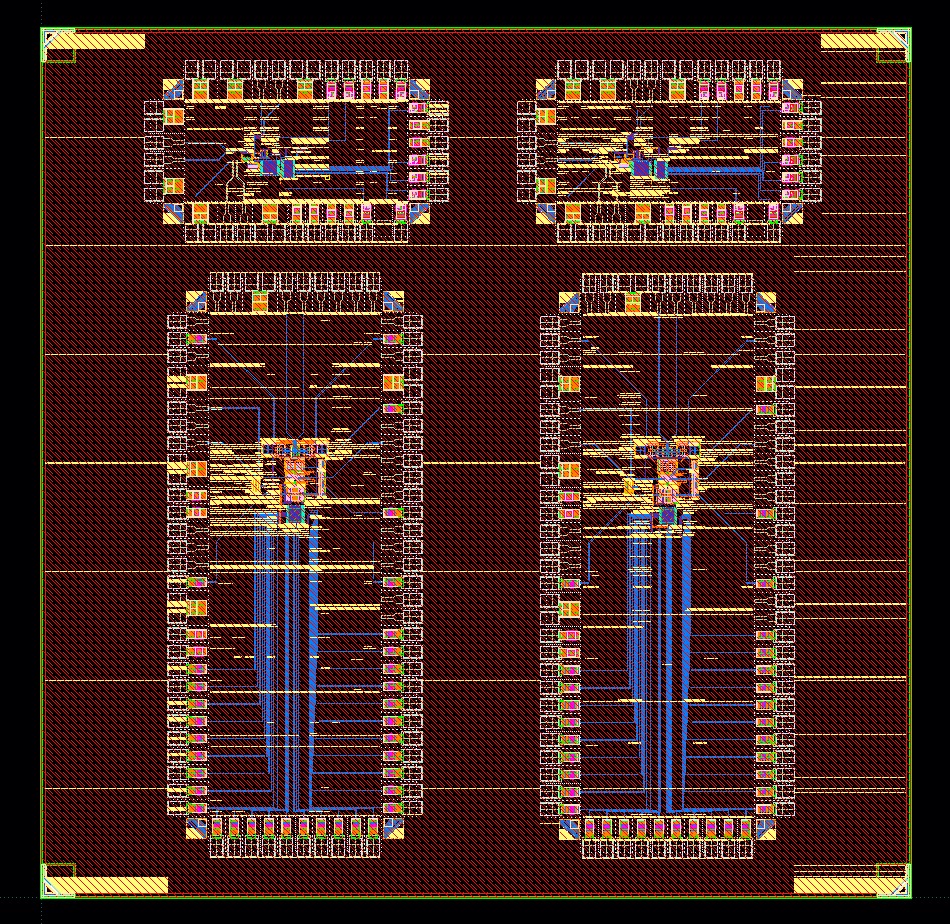

- 레이아웃 사진 -

|

|||