| IP명 | SIMO DC-DC Buck Converter Using Output-Voltage-Aware Charge Control Scheme in a 65nm CMOS Process | ||

|---|---|---|---|

| Category | Analog | Application | Power Management IC |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 0.6/1.2V |

| IP유형 | Hard IP | 동작속도 | 2.4GHz |

| 검증단계 | Silicon | 참여공정 | SS65-1902 |

| IP개요 | We designed a single inductor multiple output (SIMO) DC-DC Converter with Output Voltage Aware Charge Control (OVACC). To be used for low power application, the chip should be fabricated in a 65nm CMOS process. Using 65nm CMOS process, the expected efficiency and output voltage ripple of SIMO DC-DC Buck Converter can be achieved 92% and less than 20mV, respectively. Moreover, the best output voltage cross regulation can be obtained 0.016mV/mA when the total output power is 556mW. | ||

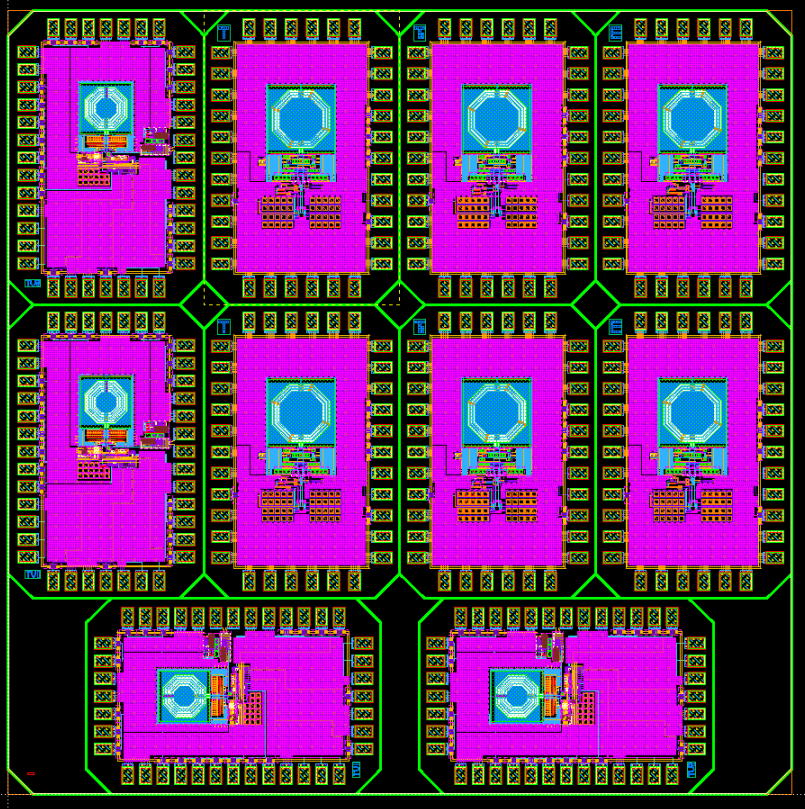

- 레이아웃 사진 -

|

|||