| IP명 | A Low-Jitter and Low-Fractional-Spur Ring-DCO-Based 5.3 GHz Fractional-N Digital PLL. | ||

|---|---|---|---|

| Category | Analog | Application | Wireless/Wireline communication |

| 실설계면적 | 3㎛ X 3㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 5000000000Hz |

| 검증단계 | Silicon | 참여공정 | HM-2301 |

| IP개요 | 고속 통신에 대한 수요가 커지면서, low jitter, low spur clock generator 의 필요성이 대두되고 있음. Q-noise 를 없애기 위해서 DTC 가 많이 사용되고 있지만, DTC의 Nonlinearity에 의한 Spur 가 문제가 되고 있음. 따라서, 본 Tapeout에서는 DTC의 2차 3차 Nonlinearity 를 제거하고 다른 회로 블락들의 Nonlinearity에 의한 Spur 또한 없애기 위해 Probability density-shpaing DSM 을 고안하여 디자인 하였음. 이를 통해, low-jitter, low-spur 를 갖는 fractional-N ring-DPLL 을 설계하였음 | ||

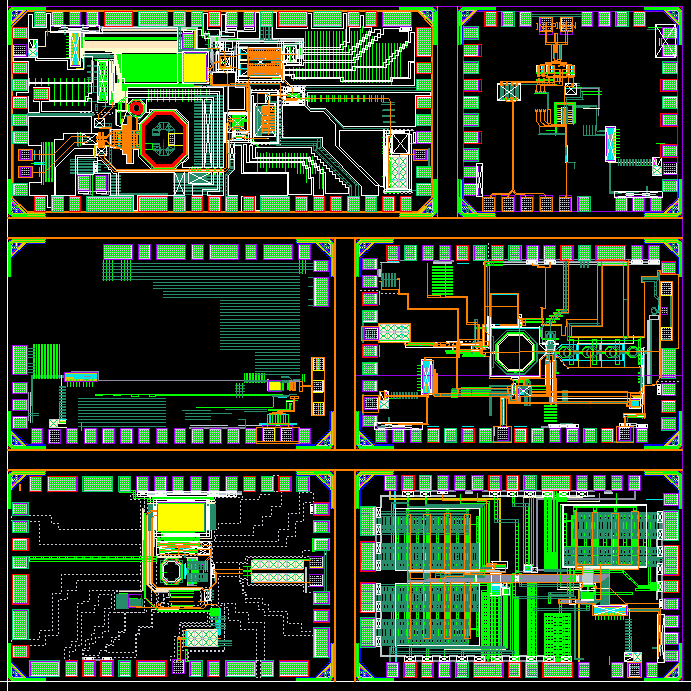

- 레이아웃 사진 -

|

|||