| IP명 |

SAR-Embedded Continuous-Time 1-0 MASH Delta-Sigma Modulator with Digital Noise Coupling Quantizer |

| Category |

Analog |

Application |

Analog to Digital Converter |

| 실설계면적 |

4㎛ X 4㎛ |

공급 전압 |

1V |

| IP유형 |

Hard IP |

동작속도 |

1GHz |

| 검증단계 |

Silicon |

참여공정 |

SF28-2301 |

| IP개요 |

본 논문은 가청 주파수 대역에서 사용되는 고해상도 analog to digital converter (ADC) 를 위한continuous time (C T) delta sigma modulator (DSM) 회로를 소개한다. 본 연구에서는 C T DSM 의 성능을 극대화하기 위해 successive approximation register (SAR) quantizer 를 이용한 L-0 multi stage noise shaping (MASH) 와 d igital noise coupling (DNC) 기법을 사용하였다 L-0 MASH 구조를 이용하여 feedback digital to analog converter (DAC) 의 설계 복잡도를 증가시키지 않고 효과적으로 quantizer 의 해상도를 증가시킬 수 있다 또한 일반적인 MASH 구조와 달리 L-0 MASH 구조는 추가 적인 noise shaping 효과를 얻을 수 없지만 DNC 를 이용하여 loop filter 의 차수를 증가시키기 않고 추가적인 noise shaping 효과를 얻을 수 있다. 본 연구에서는 L-0 MASH 와 DNC 기법을 결합하고 이를 하 나의 SAR quantizer 를 이용하여 해당 구현함으로써 저전력 고해상도 A DC 를 구현할 수 있다. |

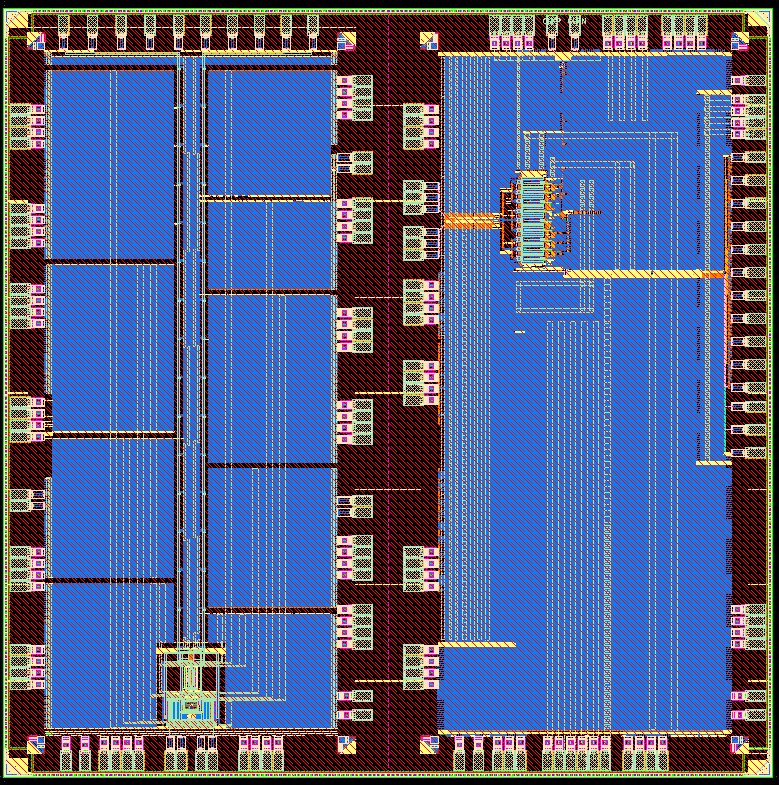

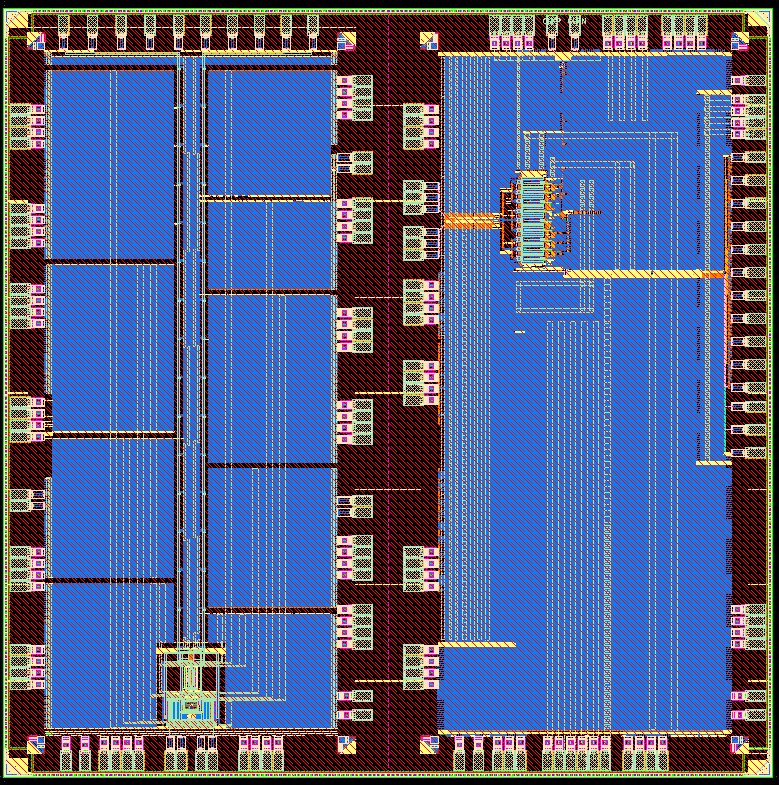

- 레이아웃 사진 -

|