| IP명 | SRAM BL Discharge Assist cells for Reducing Interconnect Resistance Effect of Write Operation in High resistance region & Wide Range And Energy Efficient Level Shifter | ||

|---|---|---|---|

| Category | Analog | Application | Foundry Application |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.2 ~ 0.3V |

| IP유형 | Hard IP | 동작속도 | 10MHz |

| 검증단계 | Silicon | 참여공정 | SS28-2202 |

| IP개요 | 공정 미세화에 따라 급격히 증가하는 저항으로 인한 SRAM 수율 저하 문제를 해결하기 위한 SRAM write assist 방법 및 주변 회로를 포함한다. Cell compatible한 구조를 cell array와 결합하여 SRAM BL discharge path를 추가하는 기법이 적용되었다. 이를 통해 고저항 환경에서 SRAM 쓰기 수율 저하를 효과적으로 완화시킬 수 있으며 고수율 및 고밀도 SRAM 구현을 가능하게 한다. SOC에서 energy 소모 감소를 위해 주로 multiple supply voltage technique를 사용한다. SRAM의 경우 yield확보를 위해 voltage scaling이 제한 되기 때문에 NTV region에서 super-thershold region의 전압 변화가 가능한 LS가 필요하다. 제안하는 LS는 wide range 동작이 가능하며, NTV region에서 발생하는 LS의 energy 소모를 split-input inverter의 사용을 통해 효과적으로 감소시킨다. |

||

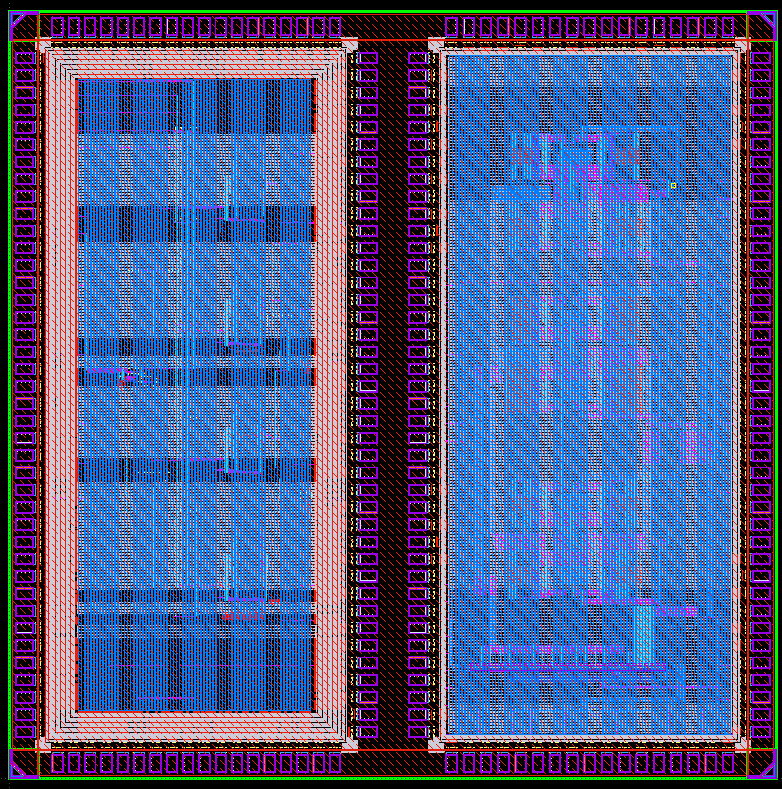

- 레이아웃 사진 -

|

|||