| IP개요 |

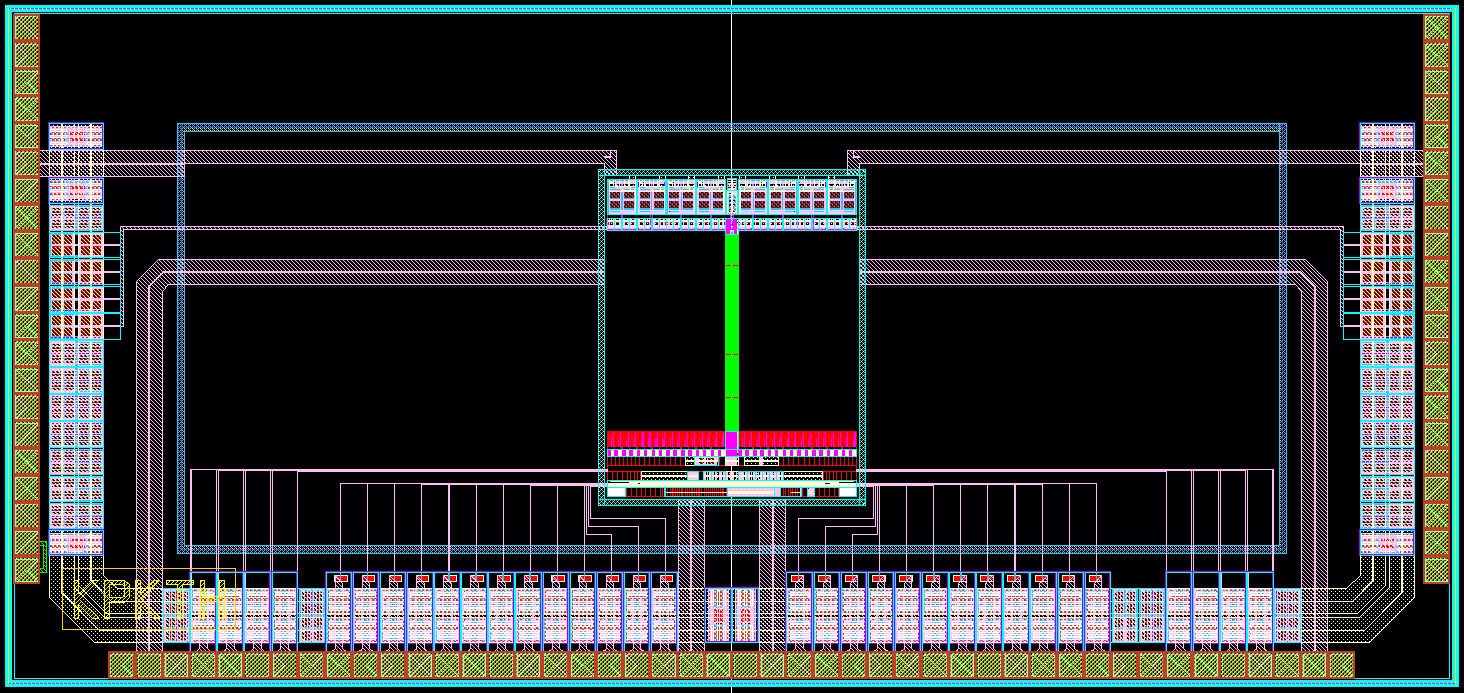

This memory designed in a 0.18-µm logic CMOS technology is an advanced 8T SRAM organized as 4096-word×8-bit, which can operate properly in subthreshold voltage regime. The bit-cell utilizes a differential swing in the read and write path, and allows an efficient column-interleaving structure. In the read operation, a column-wise assistline scheme of the cell leads to the cell being unaffected by the read disturbance. In addition, the bit-cell keeps the noise-vulnerable data ‘low’ node close to the ground level during the dummy-read operation, thus producing near-ideal voltage transfer characteristics essential for robust SRAM functionality. In the write access, the boosted wordline facilitates to change the contents of the memory bit. The memory arrays at a 0.4 V supply voltage operate with 333 kHz clock frequency while consuming an energy of 8 pJ/access. |