| IP명 | A 12b 50MS/s 0.18um CMOS SAR ADC Based on a Highly Linear C-R Hybrid DAC | ||

|---|---|---|---|

| Category | Analog | Application | AFE 회로 |

| 실설계면적 | 0.76㎛ X 0.32㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 50MHz |

| 검증단계 | Simulation | 참여공정 | MS180-1902 |

| IP개요 | 본 IP는 높은 선형성을 갖는 하이브리드 DAC을 기반의 SAR ADC이다. 입력 레인지 스케일링 기법을 이용하여 기준 전압과 입력 전압의 범위를 일치시킴으로서 추가적인 커패시터의 사용을 줄였다. 또한 공정에 덜 민감한 레이아웃 기법을 통해 oxide-gradient에 의한 오류를 줄임으로써 DAC의 선형성을 향상시킨다. | ||

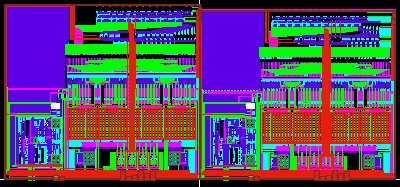

- 레이아웃 사진 -

|

|||