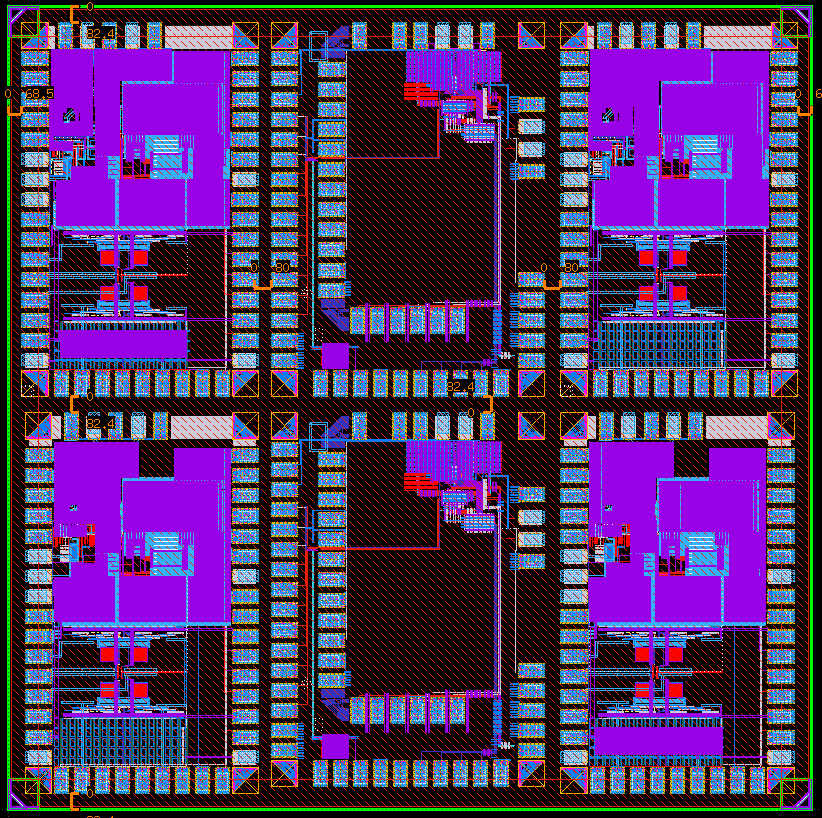

| IP개요 |

데이터 센터의 빠른 성장으로 서버 및 스위치 사이 optical interconnects의 cost 감소에 대한 요구가 크다. 이러한 optoelectronic transceiver는 대부분 off-chip photodetector를 이용하고 있는데 monolithic O/E RX를 이용하면 fabrication 및 packaging cost를 줄일 수 있다.또한 monolithic PD와 TIA를 설계하면 packaging에서 오는 parasitics를 크게 줄일 수 있고 이는 전체 O/E transceiver의 power consumption 감소나 속도 향상에 도움이 되며 APD는 자체 multiplication gain으로 높은 gain-BW product를 가지고 있기 때문에 O/E transceiver를 설계할 때 APD를 이용하는 것은 link budgeting에 도움이 된다. 이러한 이점을 가져가며, eye monitor를 통해 지속적인 eye performance를 관측한다. 이를 통해 최적의 APD bias 지점을 확인하고, on-chip voltage multiplier를 통해 해당 bias로 lock할 수 있도록 설계를 진행하였다. |