| IP명 | 1.5-bit MDAC를 사용하는 8-bit 20MSample/sec 파이프라인 아날로그 디지털 컨버터 | ||

|---|---|---|---|

| Category | Analog | Application | ADC |

| 실설계면적 | 5㎛ X 2.5㎛ | 공급 전압 | 1.8V |

| IP유형 | Hard IP | 동작속도 | 1MHz |

| 검증단계 | Simulation | 참여공정 | DB180-2101 |

| IP개요 | 본 설계에서는 1.5-bit MDAC를 사용하는 파이프라인 아날로그 디지털 컨버터(ADC)를 설계하고자한다. 제안된 ADC의 샘플링 속도는 20MSample/sec이고, 분해능은 8bit이다. 파이프라인 구조는 샘플링 속도가 빠른 것이 장점이다. ADC를 구성하는 샘플 홀드 회로와 MDAC회로는 스위치드 캐패시터 구조를 갖는다. ADC의 속도를 높이기 위해서 스위치드 캐패시터에 사용되는 연산증폭기가 큰 이득을 갖도록 하며, 높은 이득을 얻을 수 있는 폴디드 캐스코드 구조를 연산증폭기의 구조로 설계한다. | ||

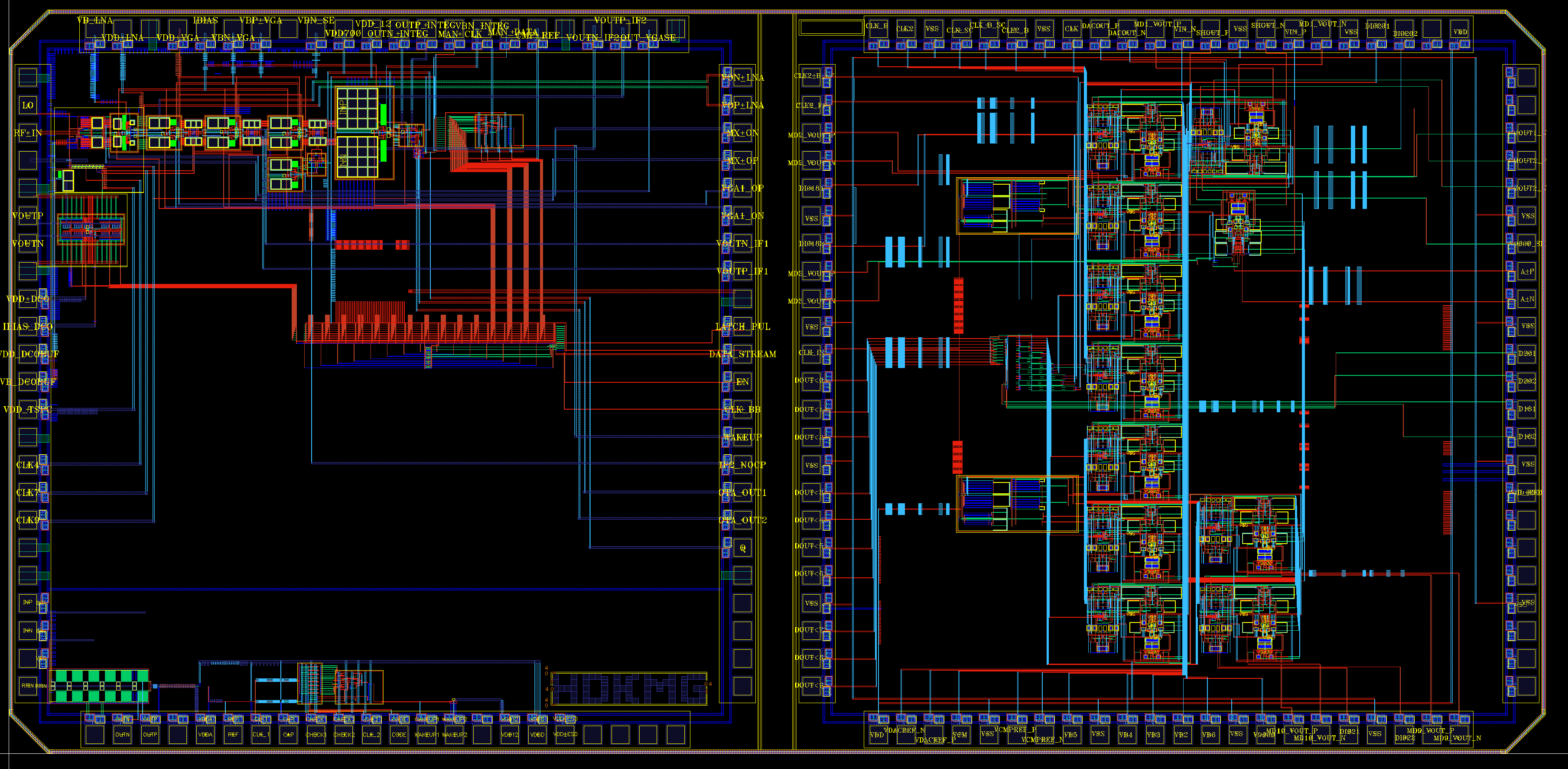

- 레이아웃 사진 -

|

|||