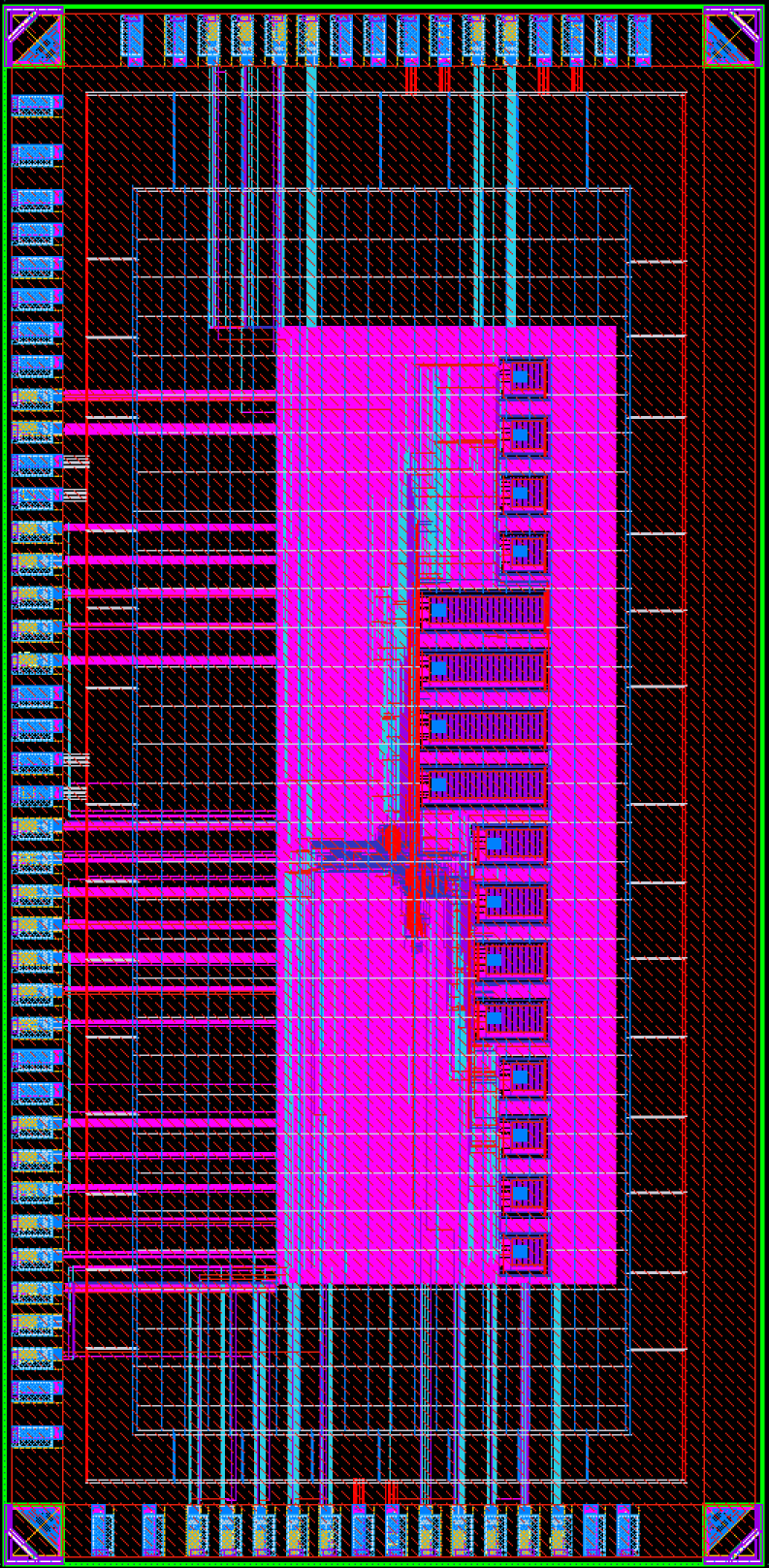

| IP개요 |

In this paper, we propose a 32-bit processor with a floating-point coprocessor. The proposed processor adopts MIPS instruction set architecture (ISA) and the coprocessor is based on posit number system. Posit number system is a floating-point representation format with the variable bit width of the exponent and fraction parts. This characteristic leads the posit numbers to represent the wider range of the numbers than IEEE 754. Moreover, the posit numbers are more accurate than IEEE 754 when the bit width of the exponent part is shorter than the bit width of the exponent bits in IEEE 754 numbers. In order to minimize the execution overhead of the coprocessor, we adopted an architecture that the operations of the coprocessor to be executed by floating-point instructions of the MIPS ISA. We fabricate the processor with Samsung 28 nm CMOS technology. Therefore, control of the coprocessor can be performed through the compiled high-level programming language. This property increases productivity because of the simplified control process. The processor operates in 3.3V, 50MHz frequency and circuit is digital type. |