| IP명 | Design of a 5 GHz CMOS VCO using a Harmonic Rejection Filter | ||

|---|---|---|---|

| Category | Analog | Application | Wireless Communication |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 3.5GHz |

| 검증단계 | Silicon | 참여공정 | SS65-2001 |

| IP개요 | 무선통신의 발달에 따라, Wi-Fi 및 LTE 등 각종 무선 통신이 널리 사용되고 있다. 그와 함께 다양한 기기들이 한정 된 주파수 대역을 나누어 사용함으로써, 간섭에 의한 문제가 나타났다. IEEE 802.11 규격의 2.4 GHz를 사용하는 Wi-Fi는 블루투스, 무선 전화 등과 주파수 대역이 근접해 있어 간섭이 일어나게 되었고 이를 해결하기 위하여, 802.11a 규격에서 5 GHz를 사용하기 시작했다. 5 GHz는 간섭이 적고, 주파수가 높아진 만큼 데이터 전송률 또한 높아졌지만, 그만큼 데이터의 안전성을 확보의 필요성이 생겼다. 따라서, 이번 연구에서는 이러한 5 GHz 무선 통신에서 안정적으로 데이터 전송 비트를 늘릴 수 있도록 고조파 제거 필터를 추가 한 Voltage Controlled Oscillator (VCO)를 설계하였으며, 65-nm의 RF CMOS process(Samsung)를 사용하여 설계하였다. 제안하는 filter는 capacitor와 bonding wire의 inductance를 이용하였으며, 설계 전압은 1.8 V, 동작 주파수는 5.4 GHz ~ 4.8 GHz, 회로 타입은 Mixed 타입으로 설계 되었다. |

||

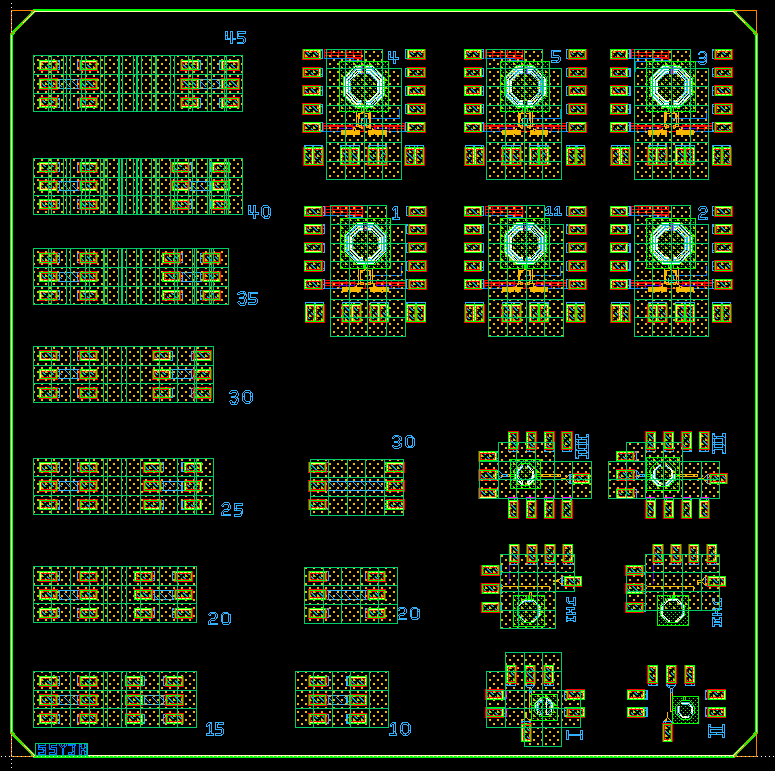

- 레이아웃 사진 -

|

|||