| IP명 | An 82fsrms-Jitter 102GHz W-Band PLL Using a Power-Gating Injection-Locked Frequency-Multiplier-Based Phase Detector | ||

|---|---|---|---|

| Category | Analog | Application | 6G communication |

| 실설계면적 | 3㎛ X 2.21㎛ | 공급 전압 | 1.2/2.5V |

| IP유형 | Hard IP | 동작속도 | 100Hz |

| 검증단계 | Silicon | 참여공정 | HM-2101 |

| IP개요 | 최근 5G 상용화가 이루어지고 있으면서, 6G 통신에 대한 관심도가 높아지고 있음. 이러한 6G 통신의 상용화를 위해서는, 100GHz 이상의 low-jitter clock generator가 필요함. 그러나 기존의 CP-PLL이나 SSPLL 방식으로는 100GHz 이상의 주파수 대역에서 low-jitter 성능을 낼 수가 없음. 따라서, 본 Tapeout에서는 PG-ILFM-based PD를 이용한 PLL을 디자인하여, low-jitter W-band clock sysnthesizer를 디자인하여 검증하고자 진행하였음. | ||

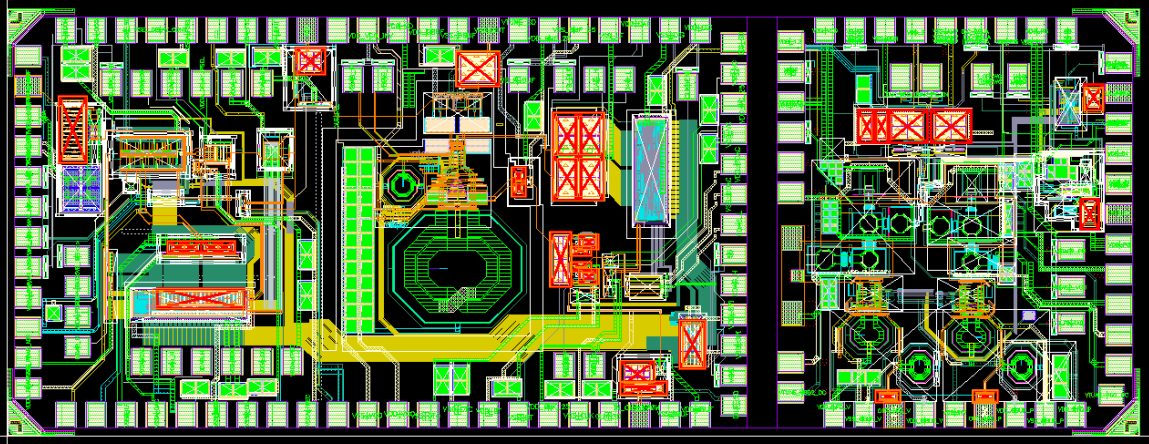

- 레이아웃 사진 -

|

|||