| IP명 | SNN 자동 인코더를 사용하는 뉴로모픽 회로 설계 | ||

|---|---|---|---|

| Category | Analog | Application | Neuromorphic computing |

| 실설계면적 | 4㎛ X 4㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 2.56MHz |

| 검증단계 | Silicon | 참여공정 | SF28-2301 |

| IP개요 | 본 설계는 부호화 기반의 SNN 자동 인코더를 사용하는 학습 뉴로모픽에 관한 칩 설계를 설명한다. 128X256 6b SRAM기반의 전류모드 신호체계는 곱셈과 덧셈을 동시에 처리한다. 또한, 순전파와 역전파 알고리즘과 가상 룩업 테이블은 제한된 볼츠만 머신의 빋지도 학습을 구현한다. 칩은 3계층으로 이루어지며 각각은 데이터를 학습하고, 16X16 2차원 픽셀을 복구하기 위한 인코더와 디코더 쌍을 의미한다. 검증은 MNIST dataset을 훈련시켜 RMS 오차와 각 시냅스의 에너지 효율을 측정한다. | ||

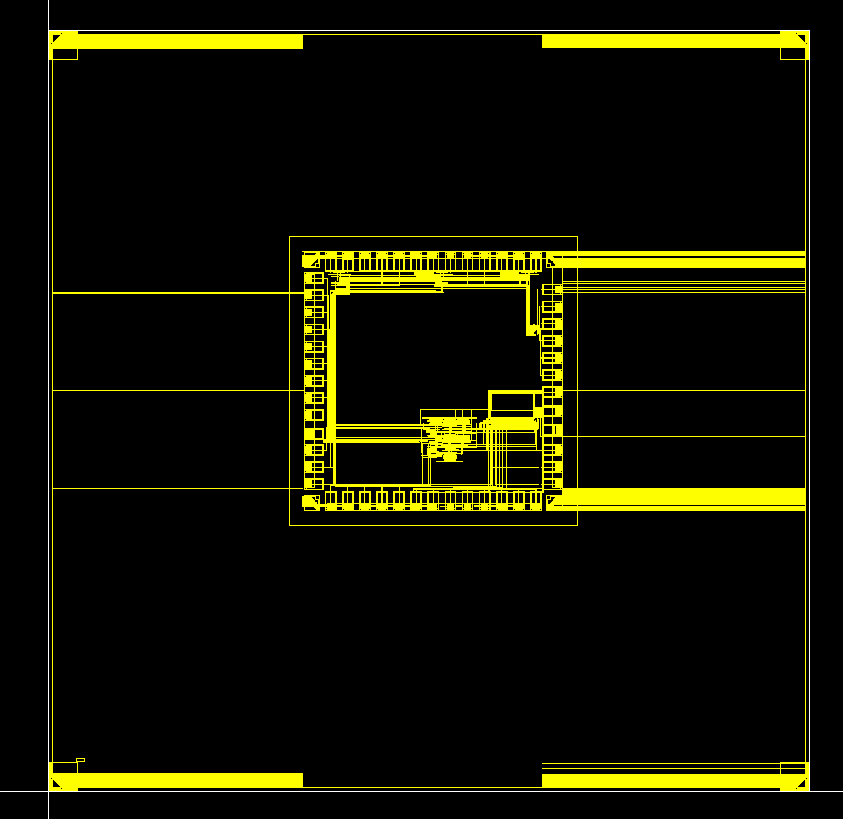

- 레이아웃 사진 -

|

|||