| IP명 | 20GHz Fractional-N Digital Phase-Locked-Loop with Reference Quadrupler | ||

|---|---|---|---|

| Category | Analog | Application | High performance LO |

| 실설계면적 | 1.7㎛ X 2㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 20GHz |

| 검증단계 | Silicon | 참여공정 | HM-2303 |

| IP개요 | 본 연구는 낮은 reference 주파수를 이용해 4배 높은 PLL의 reference 생성을 위한 reference quadrupler 및 보정 방법을 제안한다. Fractional-N 동작을 위해 고해상도 digital-to-time converter (DTC)를 설계하고, multi-point pre-distortion 기술을 이용해 비선형성을 보정한다. Reference quadrupler의 offset error로 인한 성능 저하와 BBPD의 좁은 nonlinear range를 보완하기 위해 time amplifier (TA)를 구현하였고, linear driver로 DCO proportional capacitor bank를 천천히 변경하여 reference spur를 개선하였다. | ||

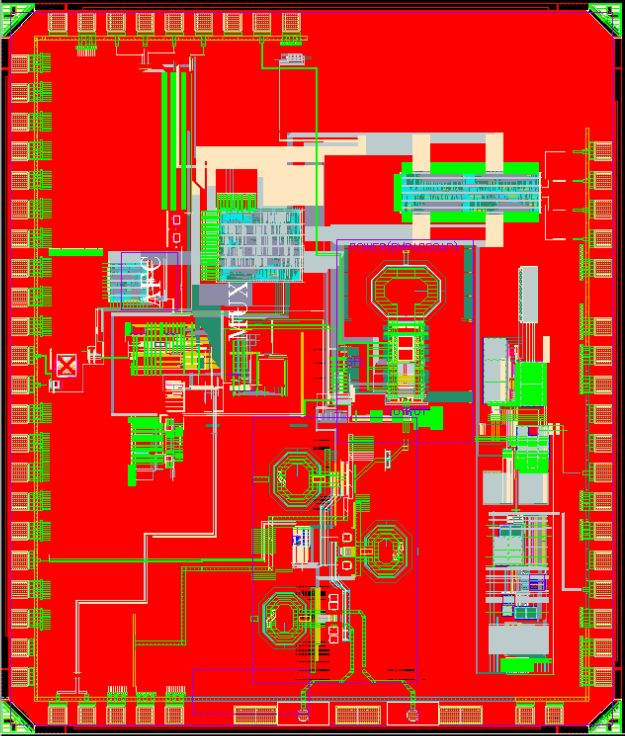

- 레이아웃 사진 -

|

|||