| IP명 | Fractional SSPD_MDLL | ||

|---|---|---|---|

| Category | Analog | Application | PLL |

| 실설계면적 | 4㎛ X 2㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 50MHz |

| 검증단계 | Silicon | 참여공정 | HM-2003 |

| IP개요 | 1.7GHz 무선통신을 위한 분수 분주 디지털 주파수 합성기(Fractional Digital PLL)를 제안한다. 디지털 클락 주파수는 기준 주파수 50MHz로 동작한다. VCO는 Accumulate Jitter에 의한 Phase noise의 증가를 해결하기 위해 주기적으로 VCO의 주파수를 기준 주파수로 Syncronous하여 Accumulator Jitter를 제거하는 MRO를 사용한다. 그러나, MRO를 사용하면 주기적으로 기준 주파수로 대체되기 때문에 Fractional divide를 하는 PLL은 심각한 Phase noise를 야기한다. 따라서, MRO를 사용하면서 Fractional divide를 할 수 있는 방법으로 DTC(Digital to Time Converter)를 사용한다. 또한 Digital PLL이므로, VCO와 ADC, DAC를 제외한 블락은 디지털 합성으로 설계하였다. | ||

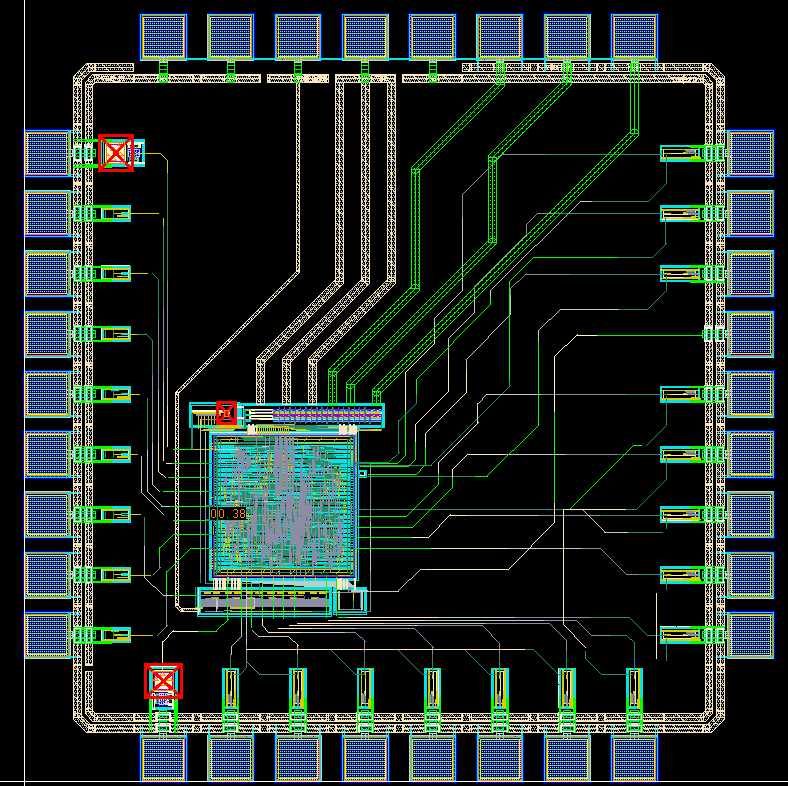

- 레이아웃 사진 -

|

|||