| IP명 | Replica Comparator-Based SS-ADC for Low-Power CMOS Image Sensor | ||

|---|---|---|---|

| Category | Mixed | Application | CMOS Image sensor |

| 실설계면적 | 4.4㎛ X 4.4㎛ | 공급 전압 | 3.3/1.8V |

| IP유형 | Firm IP | 동작속도 | 10MHz |

| 검증단계 | FPGA | 참여공정 | HM-2302 |

| IP개요 | 이미지 센서의 픽셀 피치는 고해상도 영상 촬영을 위해 점차 좁아지고 있기 때문에, 열 병렬 analog to digital converter(ADC)는 높은 집적도를 만족해야 한다. 이에 따라 single-slope ADC(SS-ADC)는 단순한 구조와 높은 선형성에 의해 이미지 센서에서 리드아웃 회로로 널리 사용되고 있다. SS-ADC는 일종의 전압-시간 변환기로, N-bit 해상도의 램프 제너레이터, 비교기, N-bit 카운터 어레이로 구성되어 있다. 램프 신호는 주변 블록에 위치한 digital to analog converter(DAC)에 의해 생성되어 모든 SS-ADC가 공유하게 된다. 따라서 좁은 픽셀 피치의 하나의 열 안에는 하나의 비교기와 카운터 어레이만 구현된다. 그러나 이러한 구조의 SS-ADC는 에너지 소비 측면에서 문제점을 가지고 있다. 특히 카운터 블록은 전압-시간 변환 동작 동안 비교기 출력인 플립 신호에 의해 트리거될 때 까지 연속적으로 토글링을 한다. 이는 픽셀 전압이 램프 전압과 동일함을 의미한다. 따라서 카운터의 신호 의존적인 토글링은 픽셀 전압과 램프 전압이 늦게 만날수록, 즉 고조도의 경우일수록, 큰 동적 전력 소비를 유발한다. 다른 큰 전력 소비 블록은 비교기이다. 비교기는 픽셀 전압과 램프 전압은 둘이 교차하는 지점에서 플립되는 출력 신호를 생성한다. 카운터는 이 플립 신호에 의해 제어되므로 SS-ADC의 유효 신호는 이 교차 지점에서만 발생한다. 그러나 광 신호는 시간에 따라 변하기 때문에 교차 지점은 항상 일정하지 않아 비교기는 항상 켜져 있어야 한다. 따라서 전압- 시간 변환 동작동안 완전히 활성화된 비교기는 SS-ADC의 에너지 효율을 저하시킨다. 이러한 SS-ADC의 단점을 극복하기 위하여, capacitive degeneration 기법을 활용한 dynamic source follower의 구조가 제안되었다 [9]. 제안된 구조는 SS-ADC에서 비교기의 정적 전류 소비를 완전히 제거하고 동적 비교기에 의해 동작하므로 에너지 효율을 극대화한다. 그러나 동적 비교기 구조는 충전과 방전에 의해 동작하므로 클럭 주파수에 크게 영향을 받는다. 또한 SS-ADC는 N-bit 데이터 변환을 위해 2N의 변환 주기를 필요로 한다. 위 구조는 결국 해상도에 비례하는 동작 주기에서 클럭 주파수가 증가할 수록 동적 에너지 효율이 크게 저하되는 단점을 가진다. 또 다른 연구에서는 동적 비교기를 이용하여 픽셀과 램프 전압의 교차 지점을 예측하여 유효 지점에서만 정적 비교기를 동작시켜 비교기의 에너지 효율성을 높인다. 충전과 방전을 이용한 동적 비교기 구조는 킥백 노이즈에 큰 영향을 끼친다. 또한 램프 전압은 주변 블록의 하나의 램프 제너레이터에서 생성되기 때문에 모든 컬럼의 SS-ADC가 공유한다. 따라서 하나의 컬럼에서 발생된 킥백 노이즈를 공유된 다른 컬럼의 SS-ADC에 영향을 주지 않기 위해선 컬럼마다 하나의 아날로그 버퍼를 추가하여야 한다. 이는 픽셀의 해상도가 증가할수록 더욱 큰 에너지 소모를 야기하므로 위의 구조 또한 큰 에너지 효율성을 가질 수 없다. 따라서 본IP연구에서는 레플리카 비교기를 활용하여 카운터의 예측 신호를 추려내어 효과적인 파워 소모를 이룬다. 또한 비교기 또한 제안하는 저전력 구조를 활용하여 플립 신호가 나온 이후로는 전력을 더이상 소모하지 않도록 만든다. 본 연구를 통해 전력 절감은 약 65.1%를 감소시키게 된다. |

||

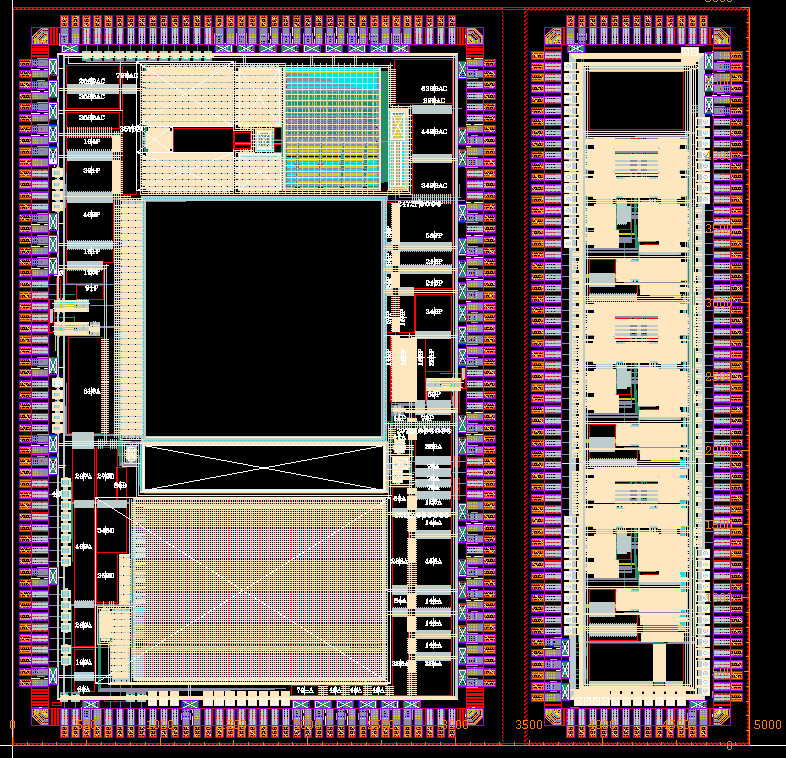

- 레이아웃 사진 -

|

|||