| IP명 | Bidirectional shift-register using Novel bidirectional pulsed-latch | ||

|---|---|---|---|

| Category | Analog | Application | Digital |

| 실설계면적 | 3㎛ X 3㎛ | 공급 전압 | 1.2V |

| IP유형 | Hard IP | 동작속도 | 100MHz |

| 검증단계 | Simulation | 참여공정 | SS65-1902 |

| IP개요 | This paper proposes an area-efficient bidirectional shift-register using bidirectional pulsed-latches. The proposed bidirectional shift-register reduces the area and power consumption by replacing master-slave flip-flops and 2-to-1 multiplexers with the proposed bidirectional pulsed-latches and non-overlap delayed pulsed clock signals, and by using sub shiftregisters and extra temporary storage latches. A 256-bit bidirectional shift-register was fabricated using a 65nm CMOS process. Its area was 1,943μm2 and its power consumption is 200μW at a 100MHz clock frequency with VDD=1.2V. It reduces area by 39.2% and power consumption by 19.4% compared to the conventional bidirectional shift-register. |

||

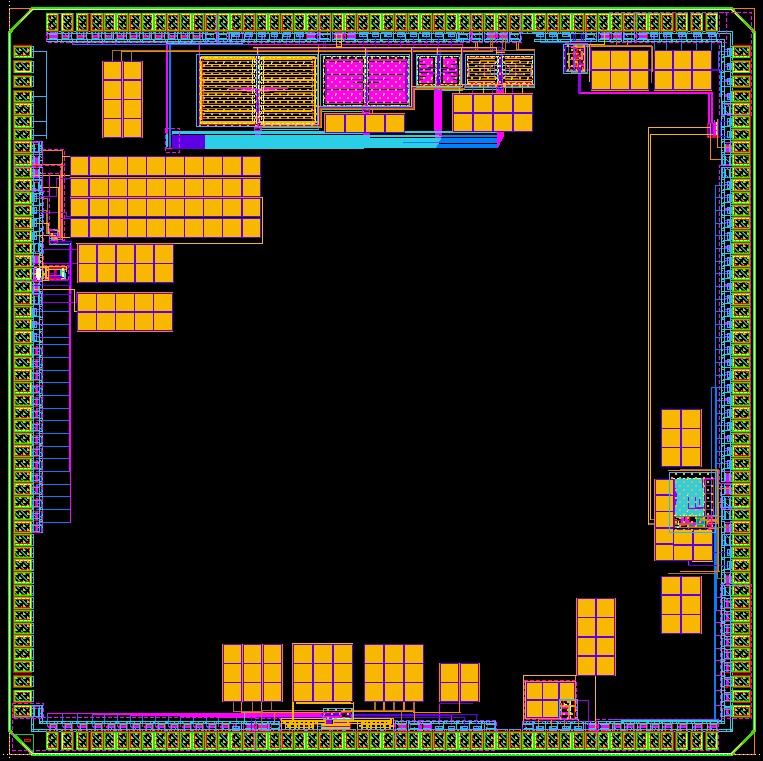

- 레이아웃 사진 -

|

|||