| IP개요 |

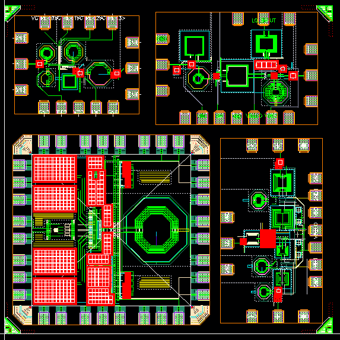

본 설계에서는 밀리미터파 5세대(5G) 위상 어레이 트랜시버에 적용 가능한 새로운 양방향 시분할 이중화(TDD) 트랜시버 시스템 및 보완 금속-산화물-반도체(CMOS) 양방향 앰프 구조를 제안한다. 제시된 양방향 증폭기는 2단계 공통 게이트 증폭기로 구성된다. 전진 및 후진 모드에서 충분한 대칭을 안전하게 얻기 위해 활성 장치와 일치하는 네트워크가 재사용된다. 또한, NMOS 바디 전압 제어를 적용하여 전진 및 후진 모드의 대칭성을 확보하고 이득을 개선합니다. 이 상보적인 금속-산화물-반도체(CMOS) 양방향 증폭기는 65 nm CMOS 기술을 사용하여 제작되었으며, 주로 5세대 신규 무선(NR) 주파수 범위 2(FR2)의 n257 및 n261 대역을 특징으로 한다. 칩 크기는 패드를 포함해 0.86mm Φ 0.57mm다. 양방향 앰프의 측정된 게인은 전진 및 후진 모드에서 10.3dB 및 10.3dB입니다. 양방향 증폭기의 측정된 노이즈 수치는 전진 및 후진 모드에서 7.2dB와 7.3dB입니다. 입력 측의 S-파라미터는 양방향으로 -10dB보다 작습니다. 출력 측의 S 파라미터는 전진 및 후진 모드에서 -9dB 및 -8.6dB입니다. 측정된 출력 1dB 전력 압축 지점은 전진 및 후진 모드에서 -1.7dBm 및 -1.2dBm입니다. 측정된 출력 3차 감청점은 정방향 및 역방향 모드에서 10.6dBm 및 10dBm입니다. 공칭 1.2V의 공급으로 35mA의 바이어스 전류를 발생시키며 활성 면적은 약 0.49mm2³입니다 |