| IP명 | A transformable DFE with dual-mode divider for low power DDR memory | ||

|---|---|---|---|

| Category | Analog | Application | 통신회로 |

| 실설계면적 | 4㎛ X 2㎛ | 공급 전압 | 1V |

| IP유형 | Hard IP | 동작속도 | 9.5GHz |

| 검증단계 | Silicon | 참여공정 | SS28-2202 |

| IP개요 | 데이터 동작 속도에 따라 half-rate와 quarter-rate의 클럭을 내보낼 수 있는 주파수 분주기를 사용하여, 저속의 데이터가 들어올 때 half-rate로 동작하여 전력 소모를 줄여줄 수 있는 수신기 회로를 설계하였다. | ||

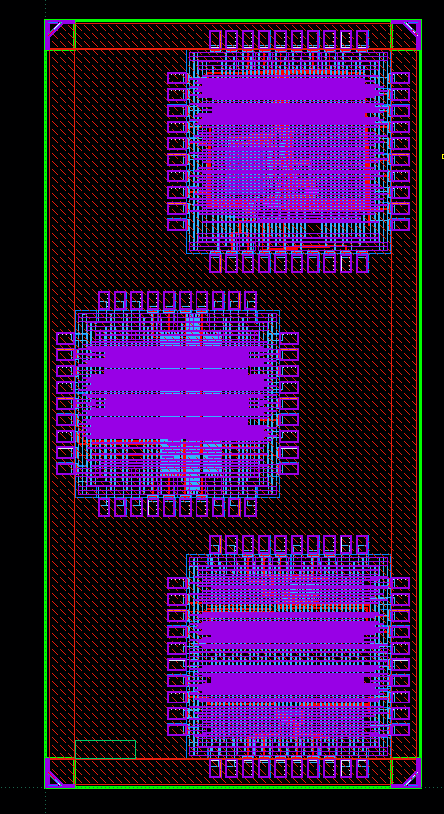

- 레이아웃 사진 -

|

|||